We recently restored an Apollo Guidance Computer1,

the computer that provided guidance, navigation, and control onboard the Apollo flights to the Moon.

This historic computer was one of the first to use integrated circuits and its CPU was built entirely from NOR gates.2

In this blog post, I describe the architecture and circuitry of the CPU.

Architecture of the Apollo Guidance Computer

The Apollo Guidance Computer with the two trays separated. The tray on the left holds the logic circuitry built from NOR gates. The tray on the right holds memory and supporting circuitry.

The Apollo Guidance Computer was developed in the 1960s

for the Apollo missions to the Moon.

In an era when most computers ranged from refrigerator-sized to room-sized, the Apollo Guidance Computer

was unusual—small enough to fit onboard the Apollo spacecraft, weighing

70 pounds and under a cubic foot in size.

The AGC is a 15-bit computer. It may seem bizarre to have a word size that isn't a power of two,

but in the 1960s before bytes became popular, computers used a wide variety of word sizes.

In the case of the AGC, 15 bits provided sufficient accuracy to land on the moon (using double- and triple-precision values as needed), so 16 bits would have increased the size and weight of the computer unnecessarily.4

The Apollo Guidance Computer has a fairly basic architecture, even by 1960s standards.

Although it was built in the era of complex, powerful mainframes, the Apollo Guidance Computer had limited performance; it is more similar to an early microprocessor

in power and architecture.3

The AGC's strengths were its compact size and

extensive real-time I/O capability. (I'll discuss

I/O in another article.)5

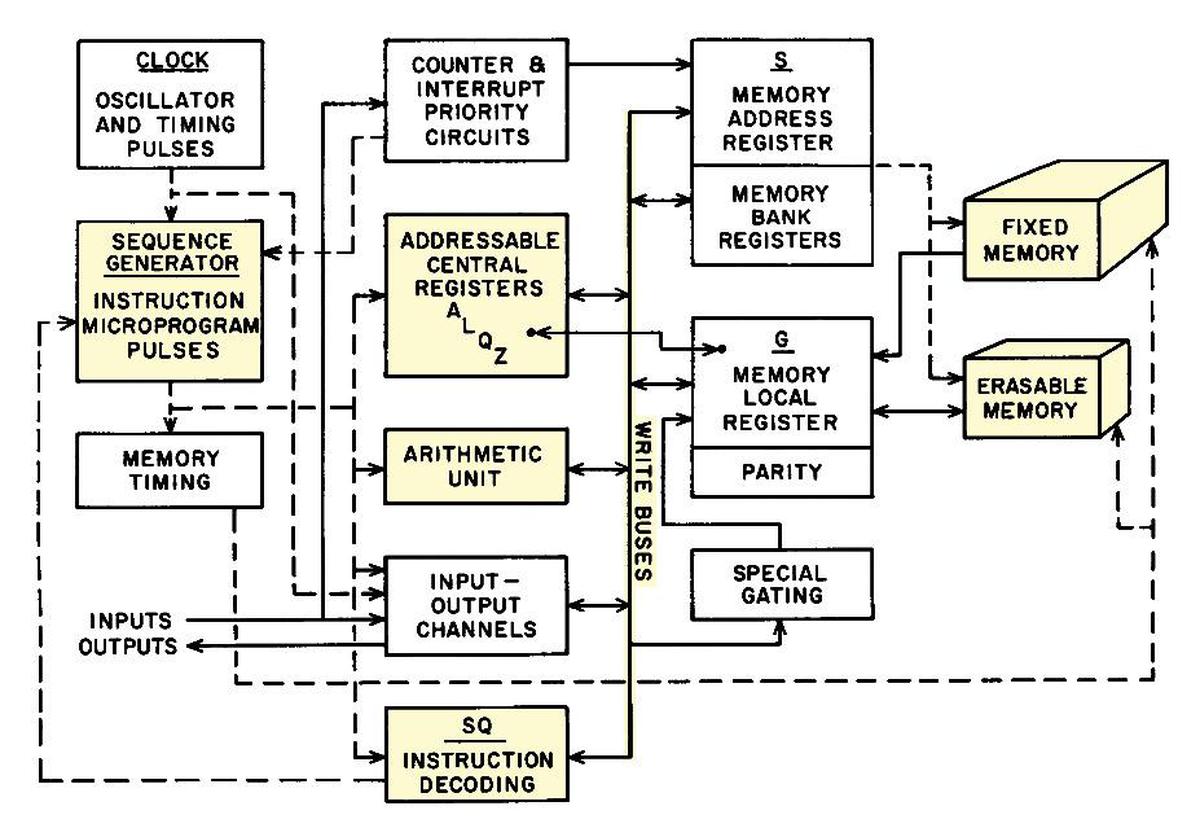

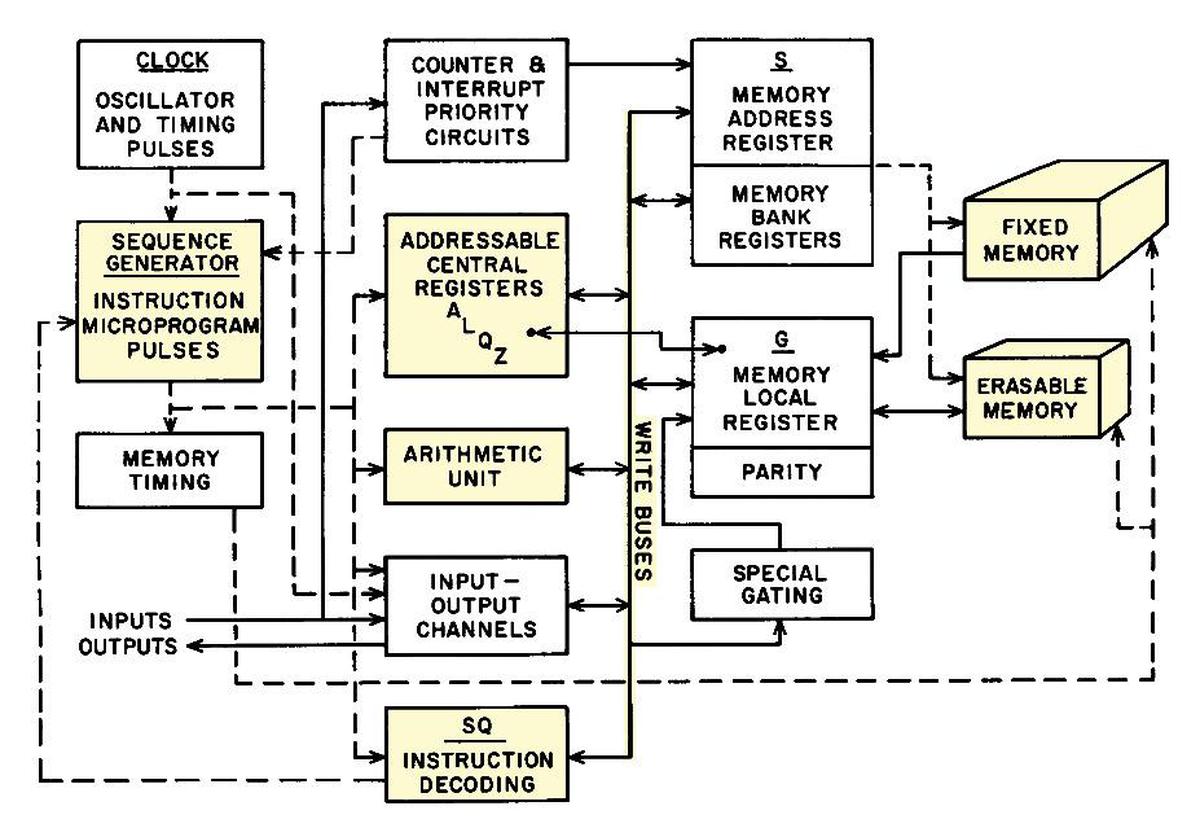

The architecture diagram below shows the main components of the AGC.

The parts I'll focus on are highlighted.

The AGC has a small set of registers, along with a simple arithmetic unit that only does addition.

It has just

36K words of ROM (fixed memory) and

2K words of RAM (erasable memory).

The "write bus" was the main communication path between the components.

Instruction decoding and the sequence generator produced the control pulses that directed the AGC.

About half of the architecture diagram is taken up by memory, reflecting that in many ways the architecture of the Apollo Guidance Computer was designed around its memory.

Like most computers of the 1960s, the AGC used core memory, storing each bit in a tiny ferrite ring (core) threaded onto a grid of wires.

(Because a separate physical core was required for every bit, core memory capacity was drastically smaller than

modern semiconductor memory.)

A property of core memory was that reading a word from memory erased that word, so a value

had to be written back to memory after each access.

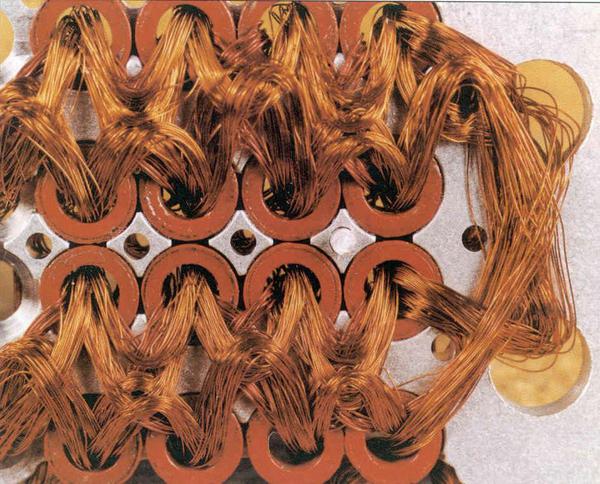

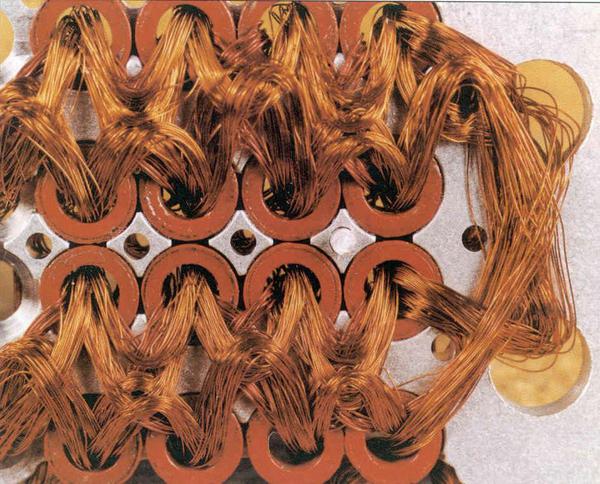

The AGC also had fixed (ROM), the famous core ropes used for program storage where bits were physically woven into the wiring pattern (below).

(I've written about the AGC's core memory

and core rope memory in detail.)

Detail of core rope memory wiring from an early (Block I) Apollo Guidance Computer.

Photo from Raytheon.

NOR gates

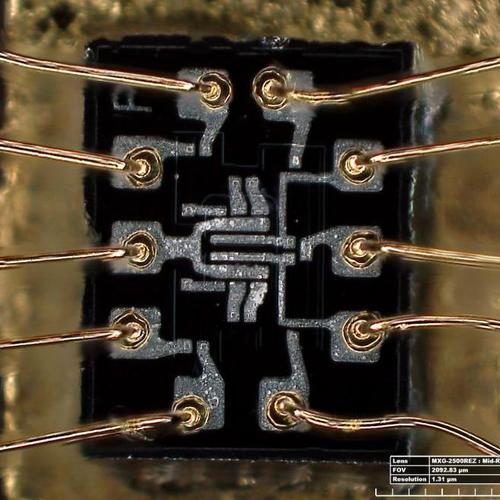

The Apollo Guidance Computer was one of the very first computers to use integrated circuits.

These early ICs were very limited;

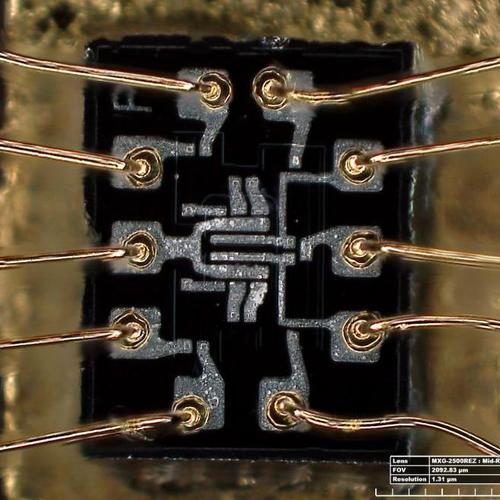

the AGC's chips (below)2

contained just six transistors and eight resistors, implementing two 3-input NOR gates.

Die photo of the dual 3-input NOR gate used in the AGC. The ten bond wires around the outside of the die connect to the IC's external pins. Photo by

Lisa Young, Smithsonian.

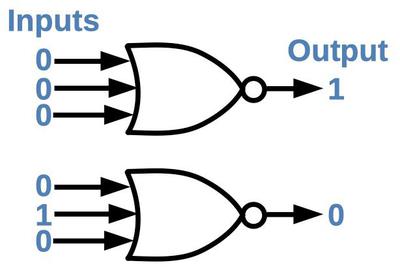

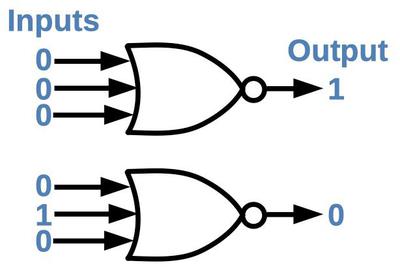

The symbol for a NOR gate is shown below. It is a very simple logic gate: if all inputs are low, the output is high.

It might be surprising that NOR gates are sufficient to build a computer, but NOR is a universal gate: you can make any other logic gate out of NOR gates.

For instance, wiring the inputs of a NOR gate together forms an inverter.

Putting an inverter on the output of a NOR gate produces an OR gate. Putting inverters on the inputs of a NOR

gate produces an AND gate.6

More complex circuits, such as flip flops, adders, and counters can be built from these gates.

The NOR gate generates a 1 output if all inputs are 0. If any input is a 1 (or multiple inputs), the NOR gate generates a 0 output.

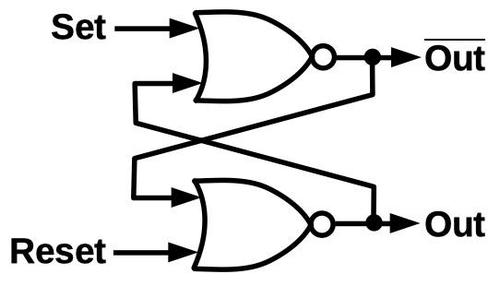

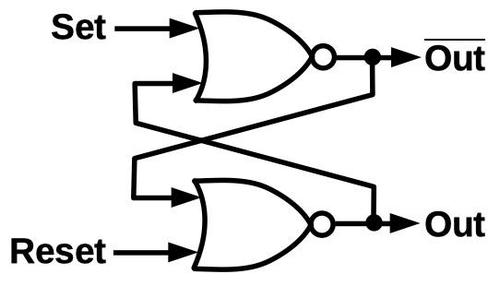

One building block that appears frequently in the AGC is the set-reset latch.

This simple circuit is built from two NOR gates and stores one bit of data: the set input stores a 1 bit and the reset input stores a 0 bit.

In more detail, a 1 pulse on the set input turns the top NOR gate off and the bottom one on, so the output is a 1.

A 1 pulse on the reset input does the opposite so the output is a 0.

If both inputs are 0, the latch remembers its previous state, providing storage.

The next section will show how the latch circuit is used to build registers.

A set-reset latch built from two NOR gates. If one NOR gate is on, it forces the other one off. The overbar on the top output indicates that it is the complement of the lower output.

The registers

The Apollo Guidance Computer has a small set of registers to store values temporarily outside of core memory. The main register is the accumulator (A), which is

used in many arithmetic operations.

The AGC also has a program counter register (Z),

arithmetic unit registers (X and Y),

a buffer register (B), return address register (Q)7, and a few others.

For memory accesses, the AGC has a memory address register (S) and a memory buffer register (G) for data.

The AGC also has some registers that reside in core memory, such as I/O counters.

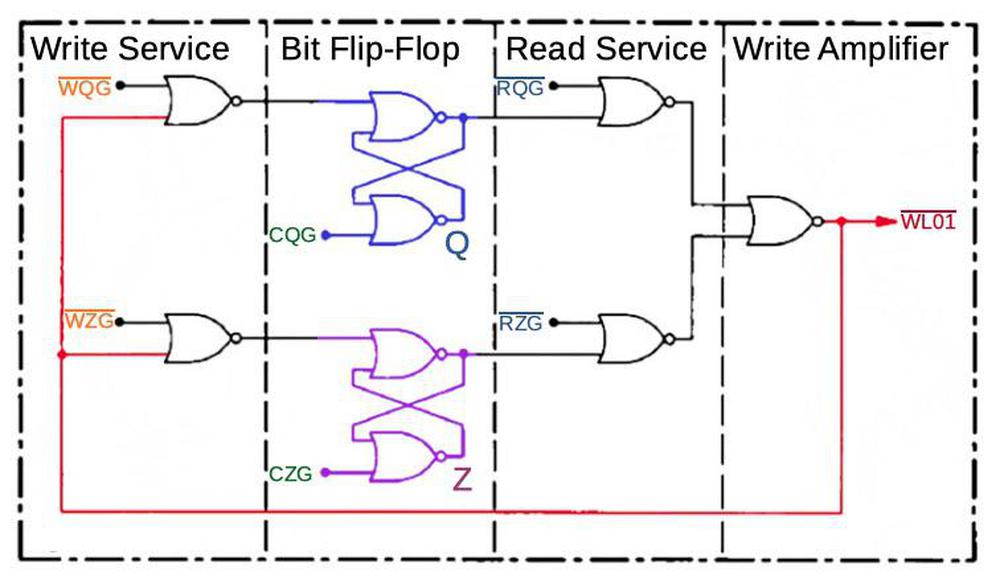

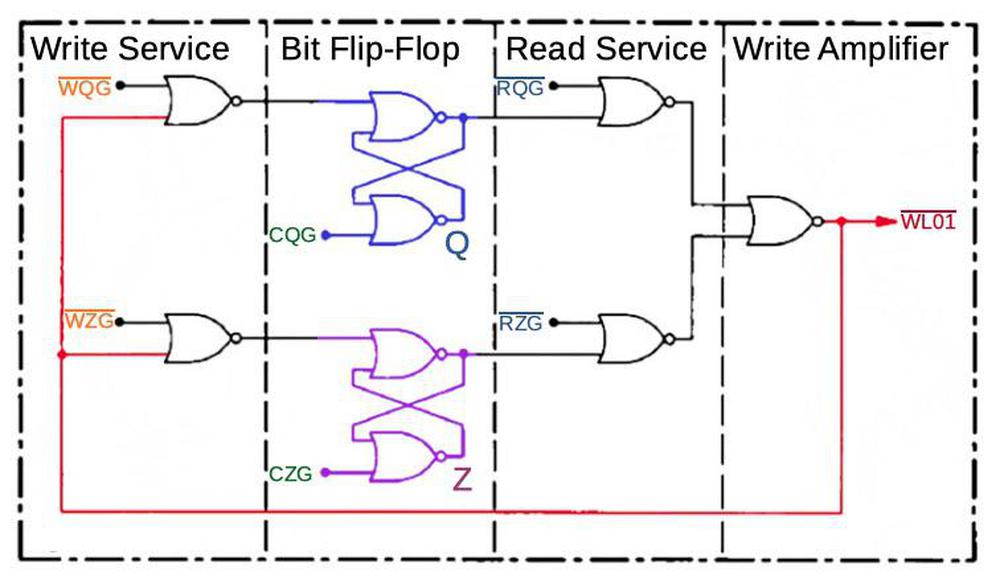

The following diagram outlines the register circuitry for the AGC,

simplified to a single bit and two registers (Q and Z).

Each register bit has a latch (flip-flop), using the circuit described earlier (blue and purple).

Data is transmitted both to and from the registers on the write bus (red).

To write to a register, the latch is first

reset by a clear signal (CQG or CZG, green).

A "write service" gate signal (WQG or WZG, orange) then allows the data on the write bus to set the corresponding register latch.

To read a register, a "read service" gate signal (RQG or RZG, cyan) passes the latch's output through the write amplifier to the write bus, for use by other parts of the AGC.

The complete register circuitry is more complex, with

multiple 16-bit registers, but follows this basic structure.

Simplified diagram of AGC register structure, showing one bit of the Q and Z registers. (

Source)

The register diagram illustrates three key points. First, the register circuitry is built from NOR gates.

Second, data movement through the AGC centers on the write bus.

Finally, the register actions (like other AGC actions) depend on specific control signals at the right time;

the "control" section of this post will discuss how these signals are generated.

The arithmetic unit

Most computers have an arithmetic logic unit (ALU) that

performs arithmetic and Boolean logic operations.

Compared to most computers, the AGC's arithmetic unit is very limited: the only operation it performs is addition

of 16-bit values, so it's called an arithmetic unit, not an arithmetic logic unit.

(Despite its limited arithmetic unit, the AGC can perform a variety of arithmetic and logic operations including multiplication and division, as explained in the footnote.9)

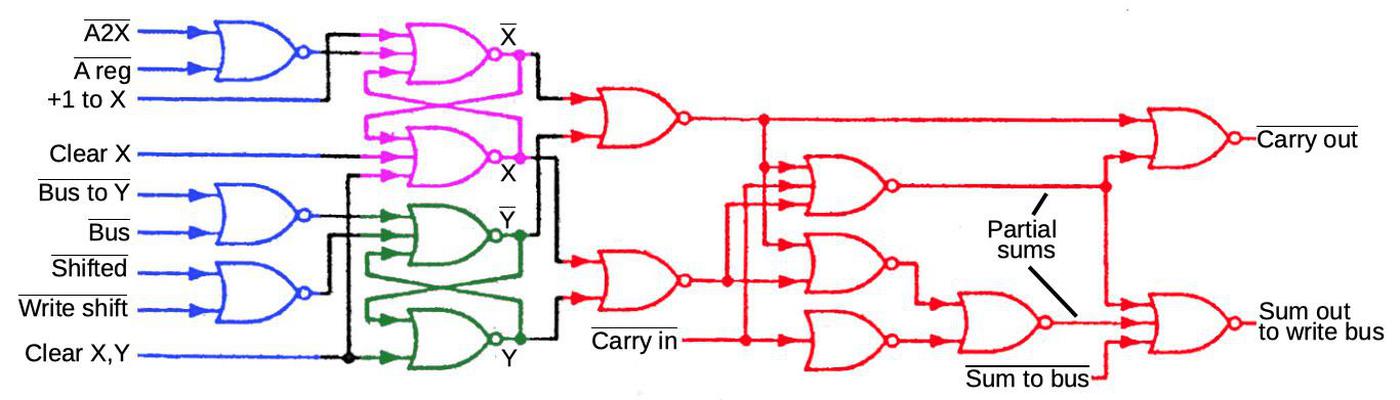

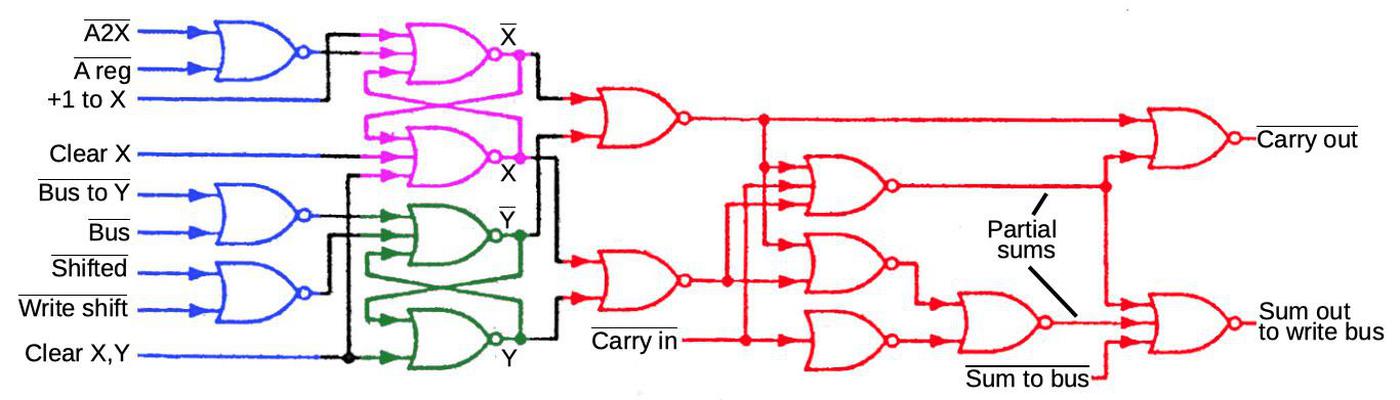

The schematic below shows one bit of the AGC's arithmetic unit.

The full adder (red)

computes the sum of two bits and a carry.

In particular, the adder sums the X bit, Y bit, and carry-in, generating the

sum bit (sent to the write bus) and carry bit.

The carry is passed to the next adder, allowing adders to be combined to add longer words.8)

Schematic of one bit in the AGC's arithmetic unit. (Based on

AGC handbook p214.)

The X register and Y register (purple and green) provide the two inputs to the adder. These are implemented with

the NOR-gate latch circuits described earlier.

The circuitry in blue writes a value to the X or Y register as specified by the control signals.

This circuitry is fairly complex since it allows constants and shifted values to be stored in the registers, but

I won't go into the details.

Note the "A2X" control signal that gates the A register value into the X register; it will be important in the following discussion.

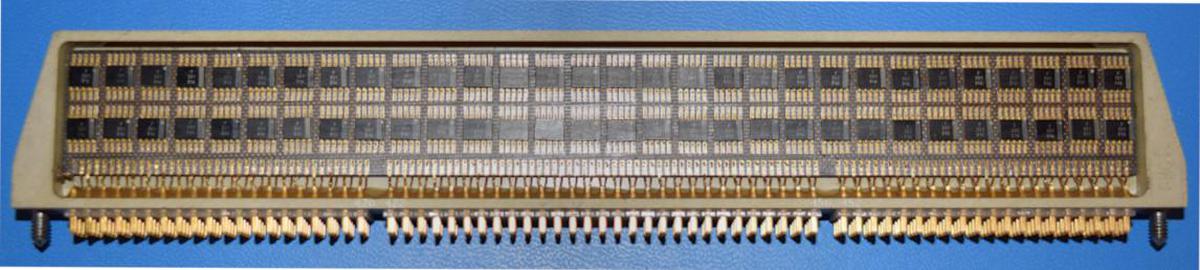

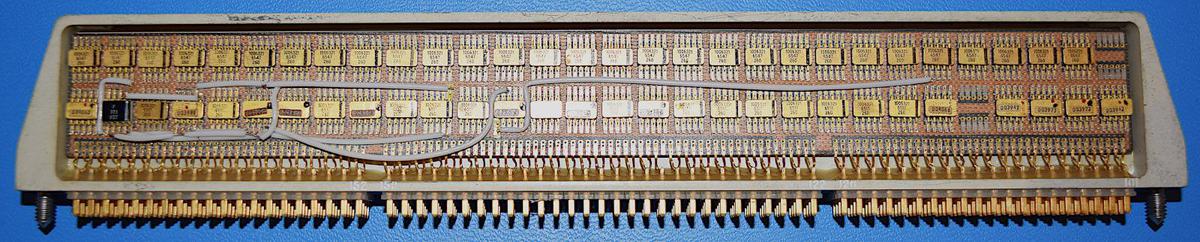

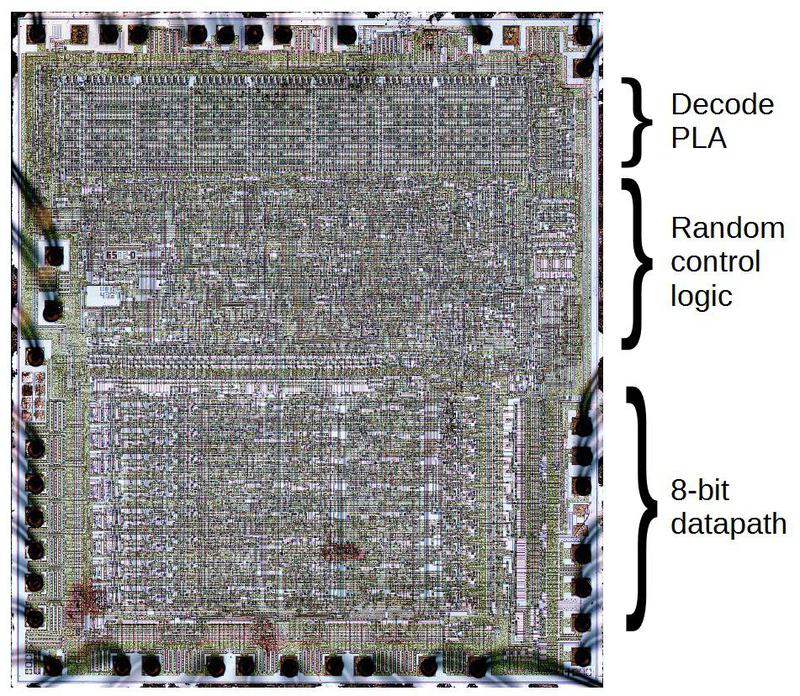

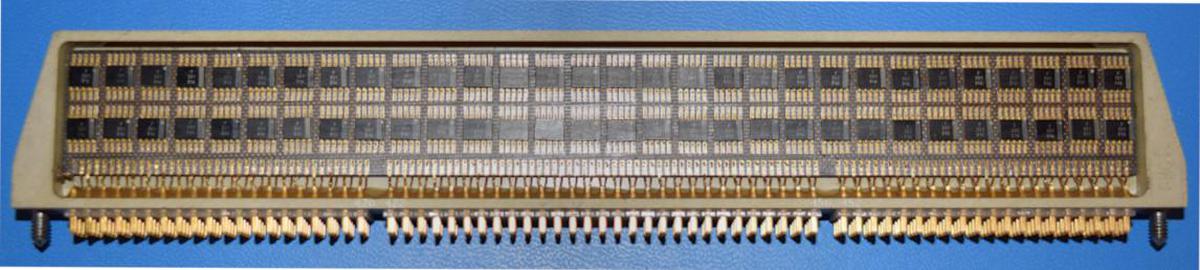

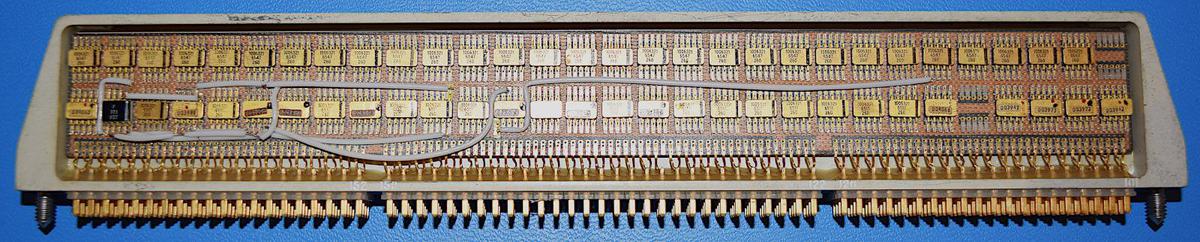

The photo below shows the physical implementation of the AGC's circuitry.

This module implements four bits of the registers and arithmetic unit.

The flat-pack ICs are the black rectangles; each module has two boards with 60 chips each, for a total of 240 NOR gates.

The arithmetic unit and registers are built from four identical modules, each handling

four bits; this is similar to a bit-slice processor.

The arithmetic unit and registers are implemented in four identical modules. Each module implements 4 bits. The modules are installed in slots A8 through A11 of the AGC.

Executing an instruction

This section illustrates the sequence of operations that the AGC performs to execute an instruction.

In particular, I'll show how an addition instruction,

ADS (add to storage), takes place.

This instruction reads a value from memory, adds it to the accumulator (A register), and stores the sum in

both the accumulator and memory.

This is a single machine instruction, but the AGC performs many steps and many values move back and forth to accomplish it.

Instruction timing is driven by the core memory subsystem.

In particular, reading a value from core memory erases the stored value, so a value

must be written back after each read. Also, when accessing core memory there is a delay between when the

address is set up and when the data is available.

The result is that each memory cycle takes 12 time steps to perform first a read and then a write.

Each time interval (T1 to T12) takes just under one microsecond, and the full memory cycle

takes 11.7µs, called a

Memory Cycle Time (MCT).

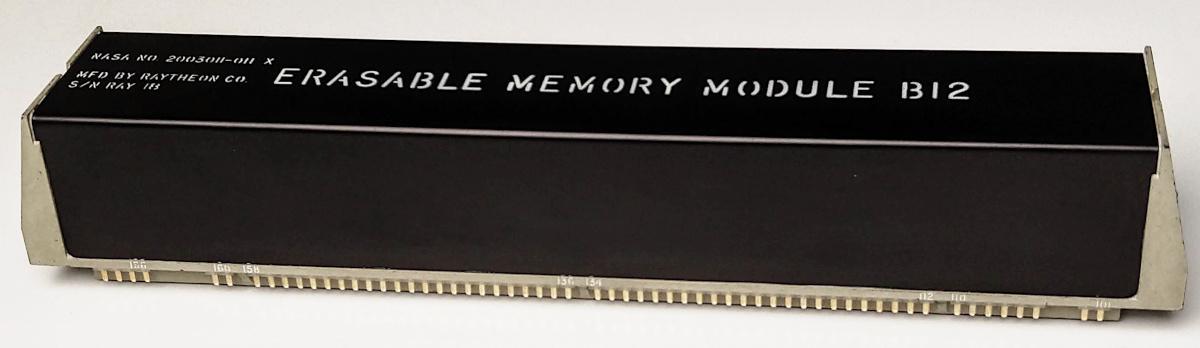

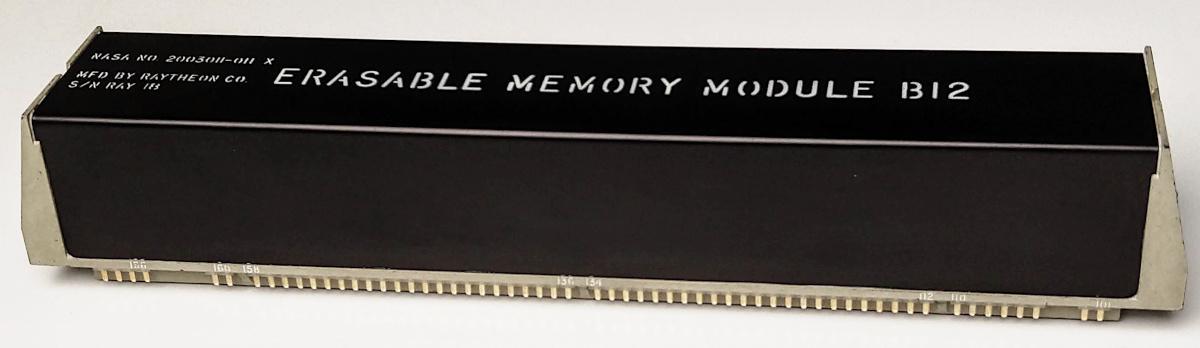

The erasable core memory module from the Apollo Guidance Computer. This module holds 2 kilowords of memory, with a tiny ferrite core storing each bit. To read memory, high-current pulses flip the magnetization of the cores, erasing the word.

The MCT is the basic time unit for instruction execution.

A typical instruction requires two memory cycles: one memory access to fetch the instruction from memory, and one

memory access to perform the operation.13

Thus, a typical instruction requires two MCTs (23.4µs), yielding about 43,000 instructions per second.

(This is extremely slow compared to modern processors performing billions of instructions per second.)

Internally, the Apollo Guidance Computer processes instructions by breaking an instruction into

subinstructions,

where each subinstruction takes one memory cycle

For example, the ADS instruction consists of two subinstructions: the ADS0 subinstruction (which does the addition) and the STD2 subinstruction

(which fetches the next instruction, and is common to most instructions).

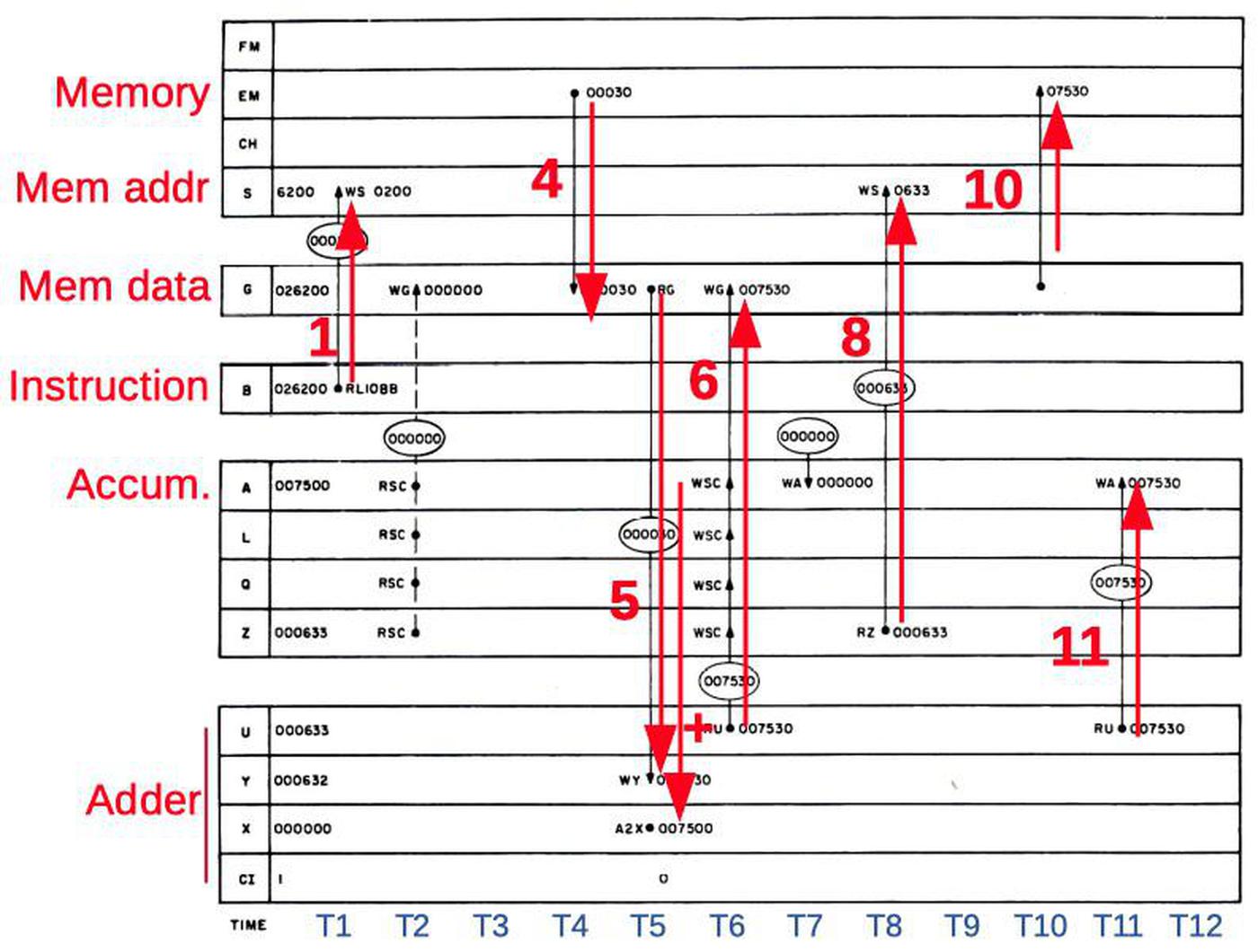

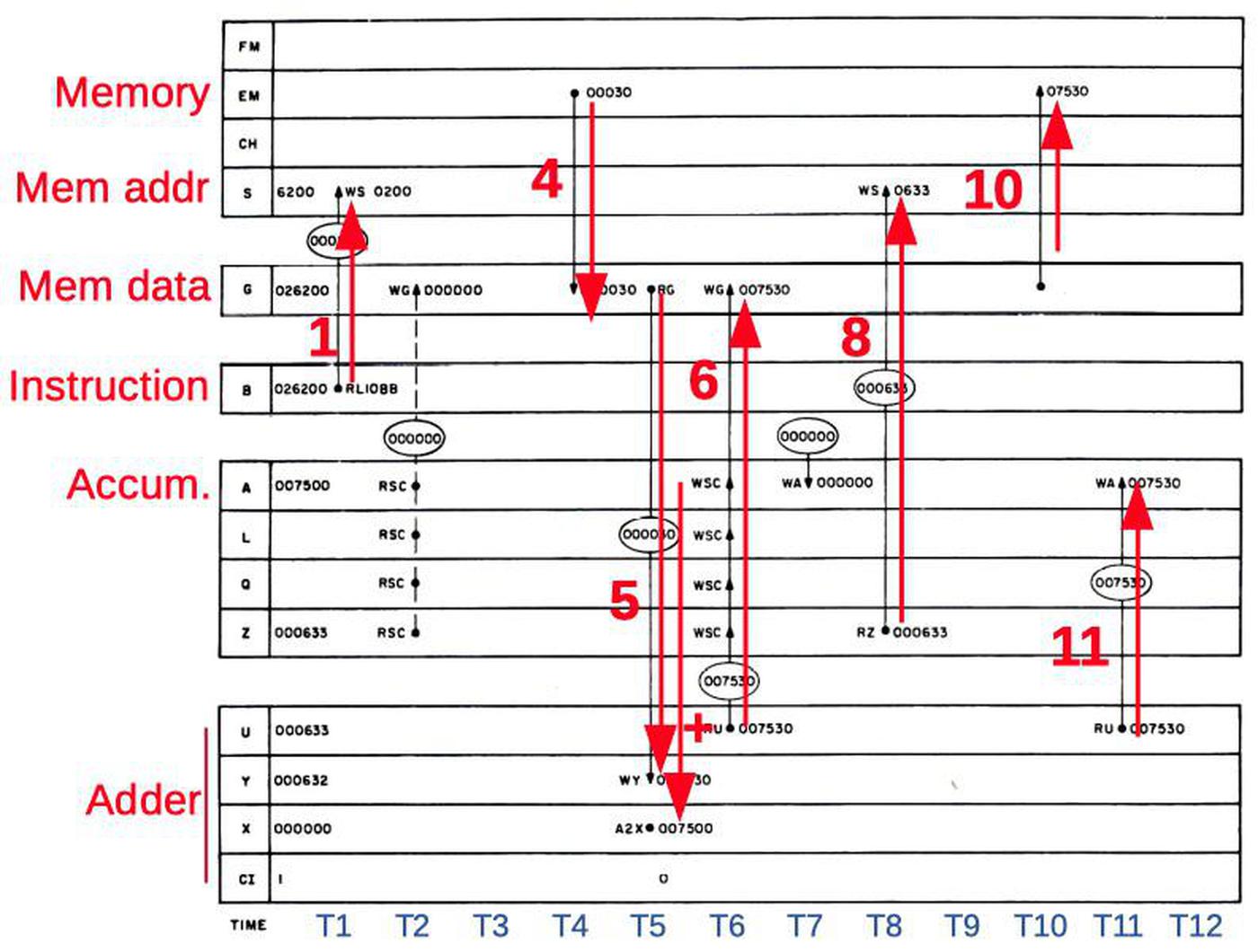

The diagram below shows the data movement inside the AGC to execute the ADS0 subinstruction.

The 12 times steps are indicated left to right.

Operations during the ADS0 (add to storage) subinstruction. Arrows show important data movement. Based on the

manual.

The important steps are:

T1: The operand address is copied from the instruction register (B) to the memory address register (S) to start a memory read.

T4: The operand is read from core memory to the memory data register (G).

T5: The operand is copied from (G) to the adder (Y).

The accumulator value (A) is copied to the adder (X).

T6: The adder computes the sum (U), which is copied to the memory data register (G).

T8: The program counter (Z) is copied to the memory address register (S) to prepare for fetching the next instruction from core memory.

T10: The sum in the memory data register (G) is written back to core memory.

T11: The sum (U) is copied to the accumulator (A).

Even though this is a simple add instruction, many values are moved around during the 12 time intervals.

Each of these actions has a control signal associated with it; for instance, the signal A2X at time T5 causes the accumulator (A) value to be copied to the X register.

Copying the G register to the Y register takes two control pulses: RG (read G) and WY (write Y).

The next section will explain how the AGC's control unit generates the appropriate control signals for each instruction, focusing on these A2X, RG, and WY control pulses needed by ADS0 at time T5.

The control unit

As in most computers, the AGC's control unit decodes each instruction and generates the control signals

that tell the rest of the processor (the datapath) what to do.

The AGC is designed with microcoded approach, but the control signals are generated from a hardwired control unit

built from NOR gates. Specifically, there are no microinstructions and the AGC does not have a control store holding microcode

(which would have taken too much physical space).12You can think of the AGC as implementing the microcode ROM with highly-optimized logic gates.

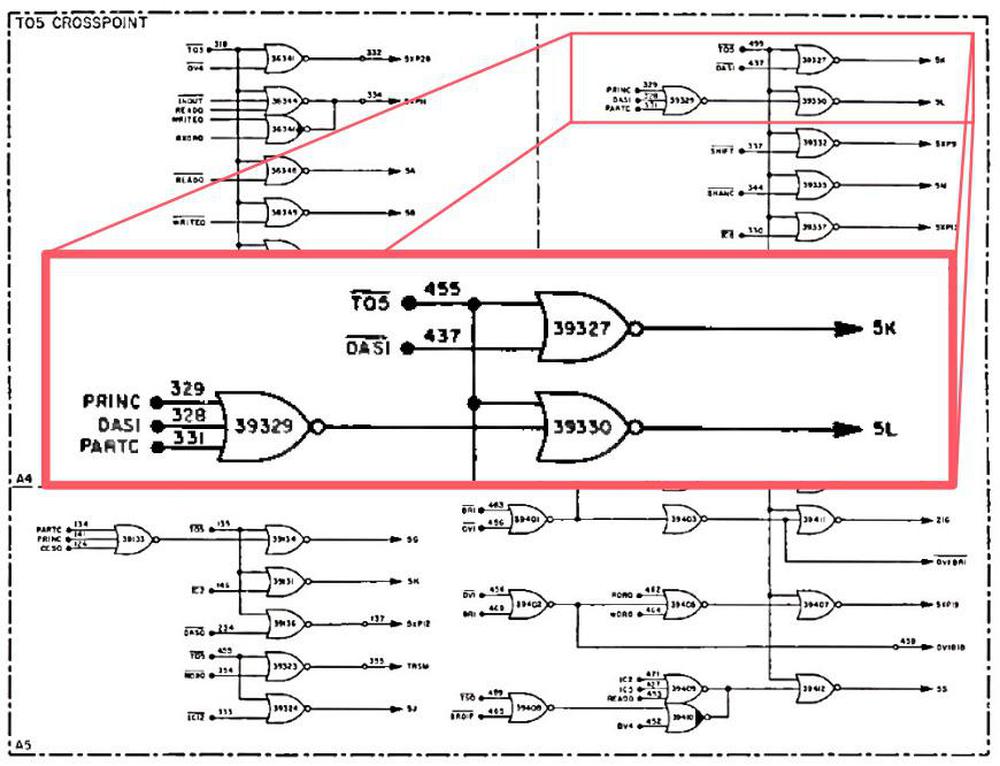

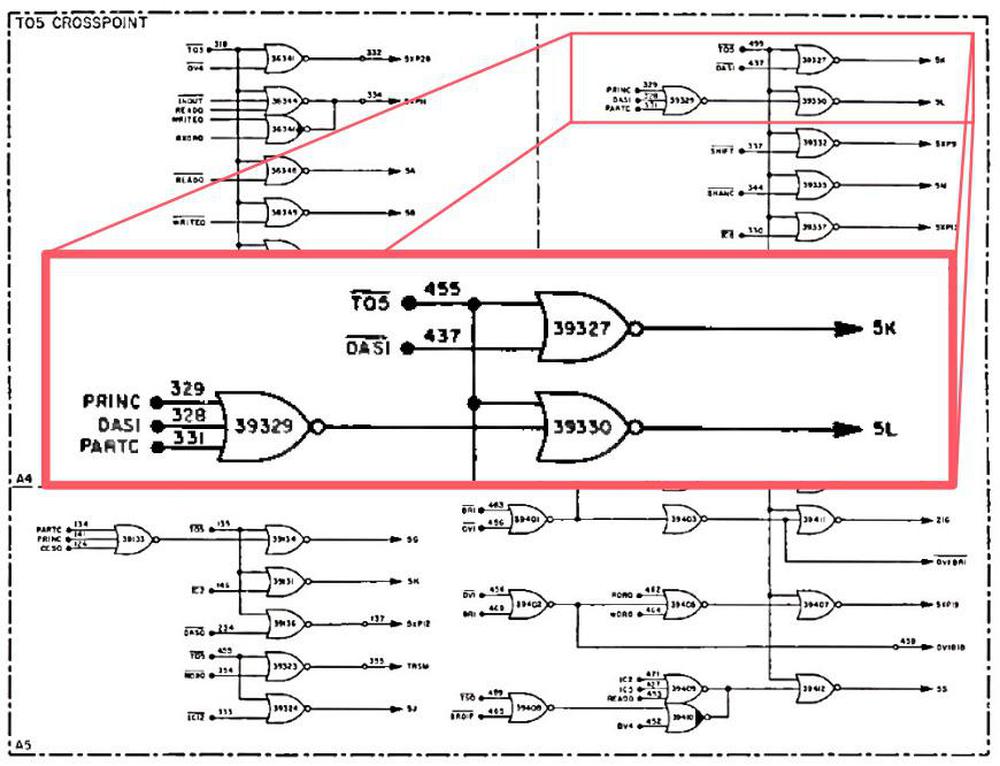

The heart of the AGC's control unit is called the crosspoint generator.

Conceptually, the crosspoint generator takes the subinstruction and the time step, and generates the control signals for that

combination of subinstruction and time step.

(You can think of the crosspoint generator as a grid with subinstructions in one direction and time steps in the other,

with control signals assigned to each point where the lines cross.)

For instance, going back to the ADS0 subinstruction, at time T5 the crosspoint generator would

generate the A2X, RG, and WY control pulses, causing the desired data movement.

The crosspoint generator required a lot of circuitry and was split across three modules; this is module A6. Note the added wires to modify the circuitry. This is an earlier module used for ground testing; modules in flight did not have these wires.

For efficiency, the implementation of the control unit is highly optimized.

Instructions with similar

behavior are combined and processed together by the crosspoint generator to reduce circuitry.

For instance, the AGC has a "Double-precision Add to Storage" instruction (DAS).

Since this is roughly similar to performing two single-word adds,

the DAS1 subinstruction and ADS0 subinstruction share logic

in the crosspoint generator.

The schematic below shows the crosspoint generator circuitry for time T5, highlighting the logic

for subinstruction ADS0 (using the DAS1 signal).

For instance, the 5K signal is generated from the combination of DAS1 and T5.

Crosspoint circuit for signals generated at time T5. With negative inputs, these NOR gates act as AND gates, detecting a particular subinstruction AND T05. From

Apollo Lunar Excursion Manual.

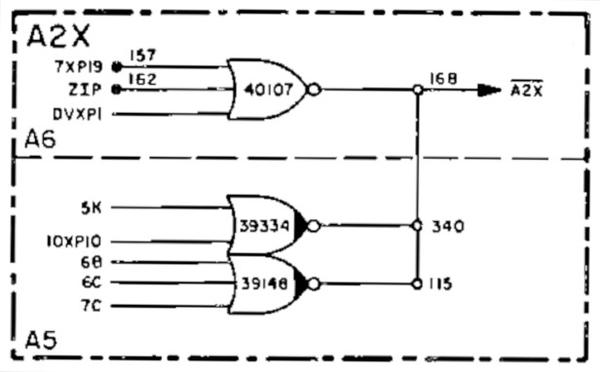

But what are the 5K and 5L signals? These are another optimization. Many control pulses often occur together, so instead

of generating all the control pulses directly, the crosspoint generates intermediate crosspoint signals.

For instance, 5K generates both the A2X and RG control pulses, while 5L generates the WY control pulse.

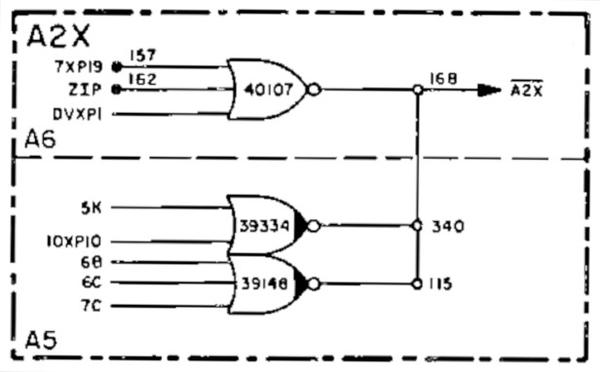

The diagram below shows how the A2X signal is generated:

any of 8 different signals (including 5K) generate A2X.15 Similar circuits generate the other control pulses.

These optimizations reduced the size of the crosspoint generator, but it was still large, split across three modules in the AGC.

The A2X control signal is generated from multiple "crosspoint pulses" from the crosspoint generator. The different possibilities are ORed together. From

manual, page 4-351.

To summarize, the control unit is responsible for telling the rest of the CPU what to do in order to execute an instruction.

Instructions are first decoded into subinstructions. The crosspoint generator creates the proper control pulses for each

time interval and subinstruction, telling the AGC's registers, arithmetic unit, and memory what to do.14

Conclusion

This has been a whirlwind tour of the Apollo Guidance Computer's CPU.

To keep it manageable, I've focused on the ADS addition instruction and a few of the control pulses

(A2X, RG, and WY) that make it operate.

Hopefully, this gives you an idea of how a computer can be built from components as primitive as NOR gates.

The most visible part of the architecture is the datapath: arithmetic unit, registers, and the data bus.

The AGC's registers are built from simple NOR-gate latches. Even though the AGC's arithmetic unit can only do addition,

the computer still manages to perform a full set of operations including multiplication and division and Boolean operations.9

However, the datapath is just part of the computer. The other critical component

is the control unit, which tells the data path components what to do. The AGC uses an approach centered around

a crosspoint generator, which uses highly-optimized hardwired logic to generate the right control pulses for

a particular subinstruction and time interval.

Using these pieces, the Apollo Guidance Computer provided guidance, navigation, and control onboard the Apollo

missions, making the Moon landings possible. The AGC also provided a huge boost to the early integrated circuit

industry, using 60% of the United States' IC production in 1963. Thus, modern computers owe a lot to the AGC and its

simple NOR gate components.

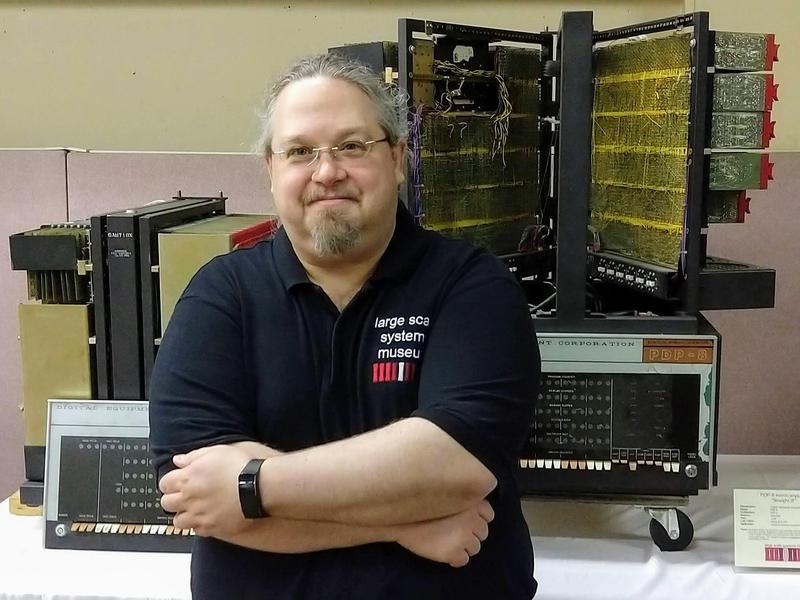

The Apollo Guidance Computer running in Marc's lab, hooked up to a vintage Tektronix scope.

CuriousMarc has a series of AGC videos which you should watch for more information on the restoration project.

I announce my latest blog posts on Twitter, so follow me @kenshirriff for future articles. I also have an RSS feed.

Thanks to Mike Stewart for supplying images and extensive information.

Notes and references