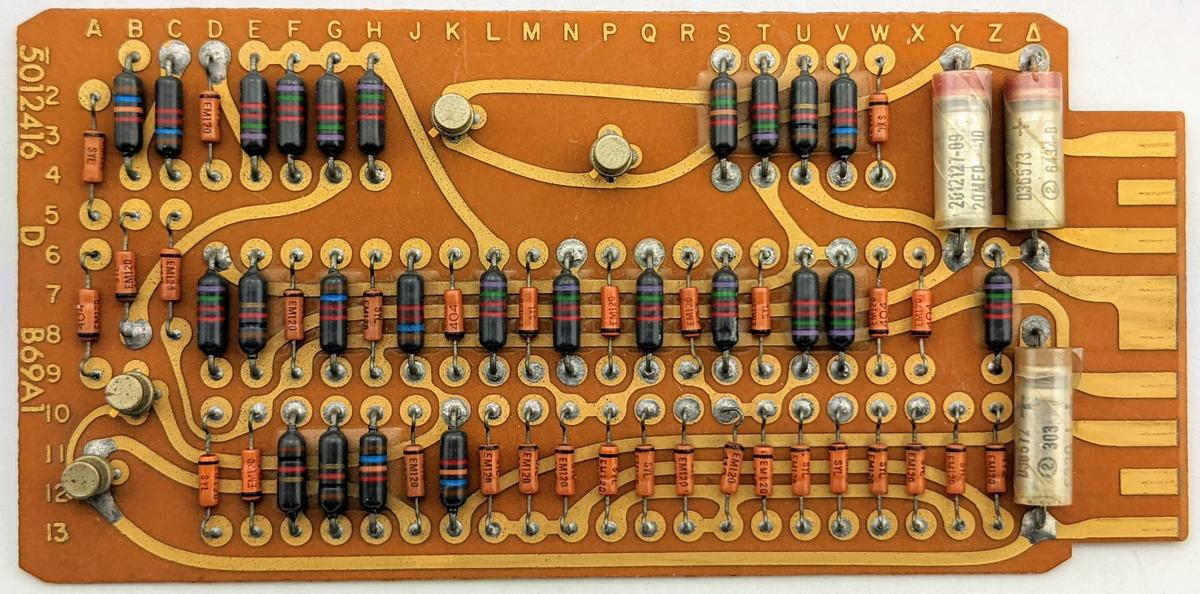

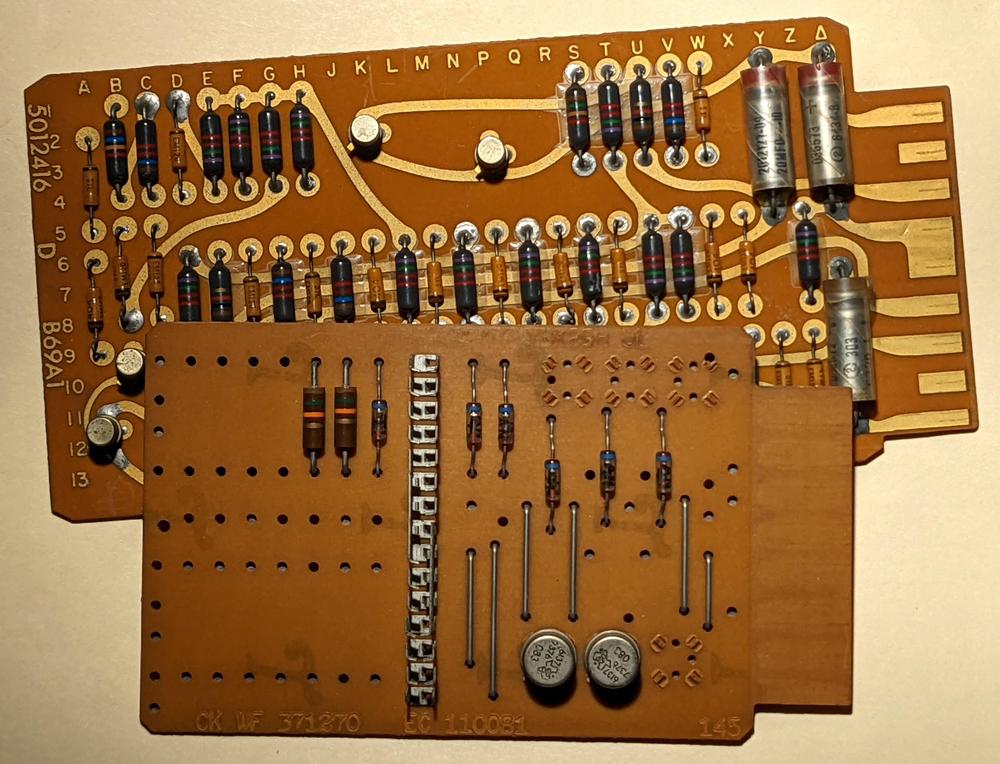

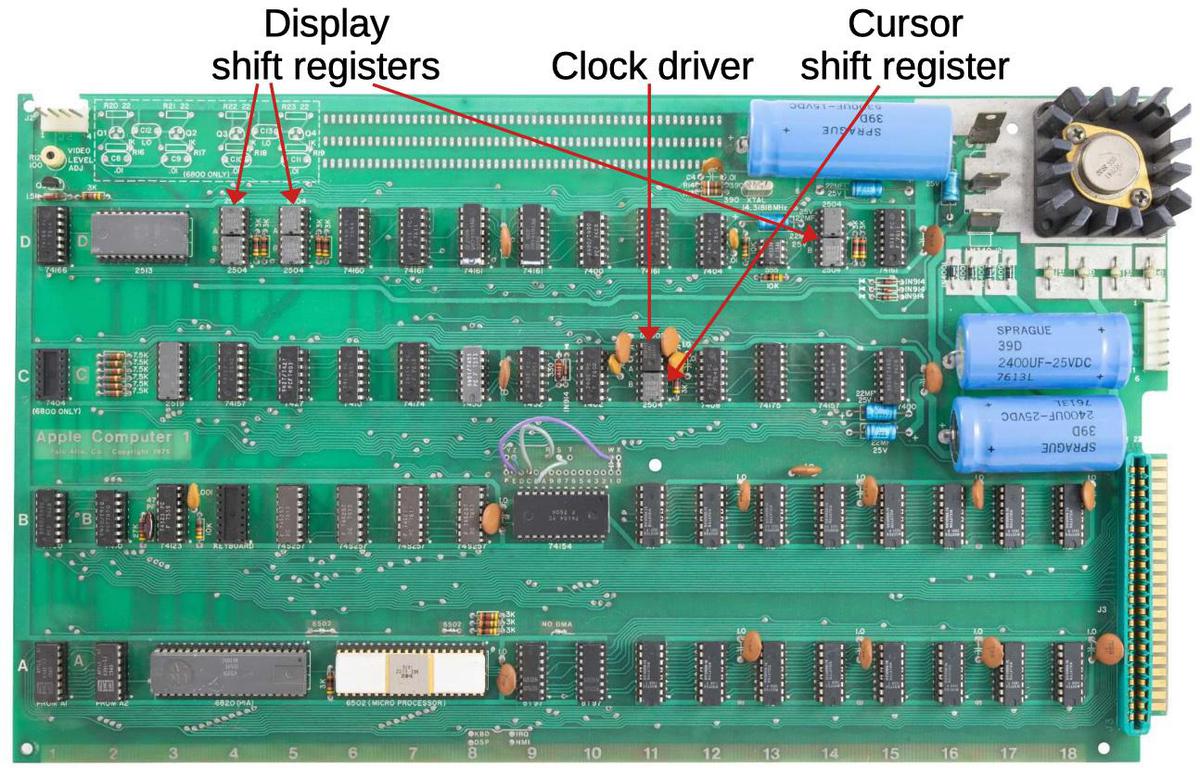

The IBM 1401 team at the Computer History Museum accumulates a lot of mystery components from donations and other sources. While going through a box, we came across the unusual circuit board below. At first, it looked like an IBM SMS (Standard Modular System) card, the building block of IBM's computers of the late 1950s and early 1960s.1 However, this board is larger, has double-sided wiring, the connector is different, and the labeling is different.2

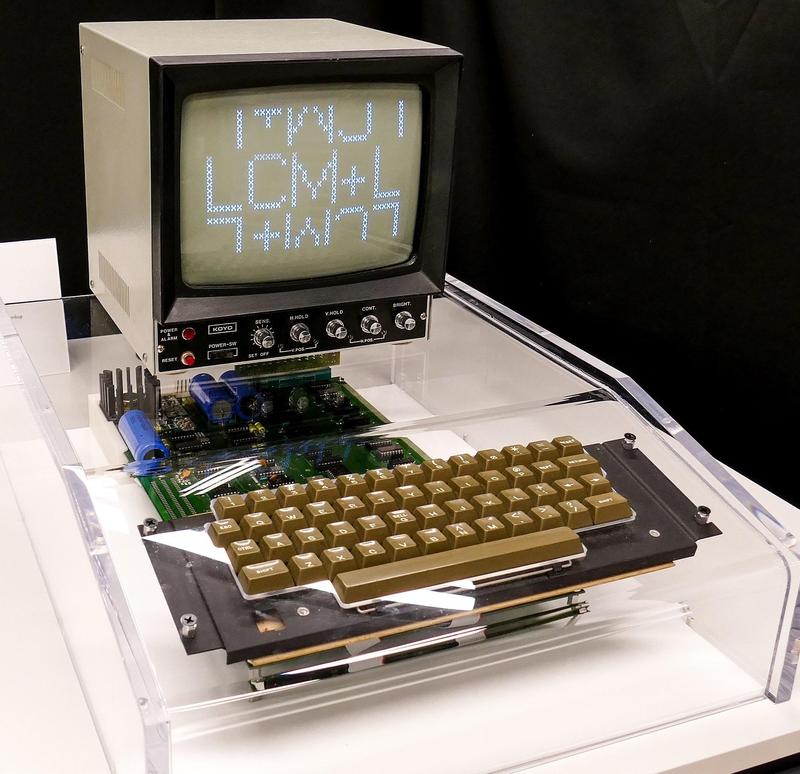

I asked around about the board and Robert Garner identified it as from the Univac 1004, a plugboard-controlled data processing system from 1963.4 The Univac 1004 was marketed as a "Card Processor" rather than a computer,3 designed for business applications that read punch cards and producing output, but still required calculation and logical decisions. Typical applications were payroll, inventory, billing, or accounting.

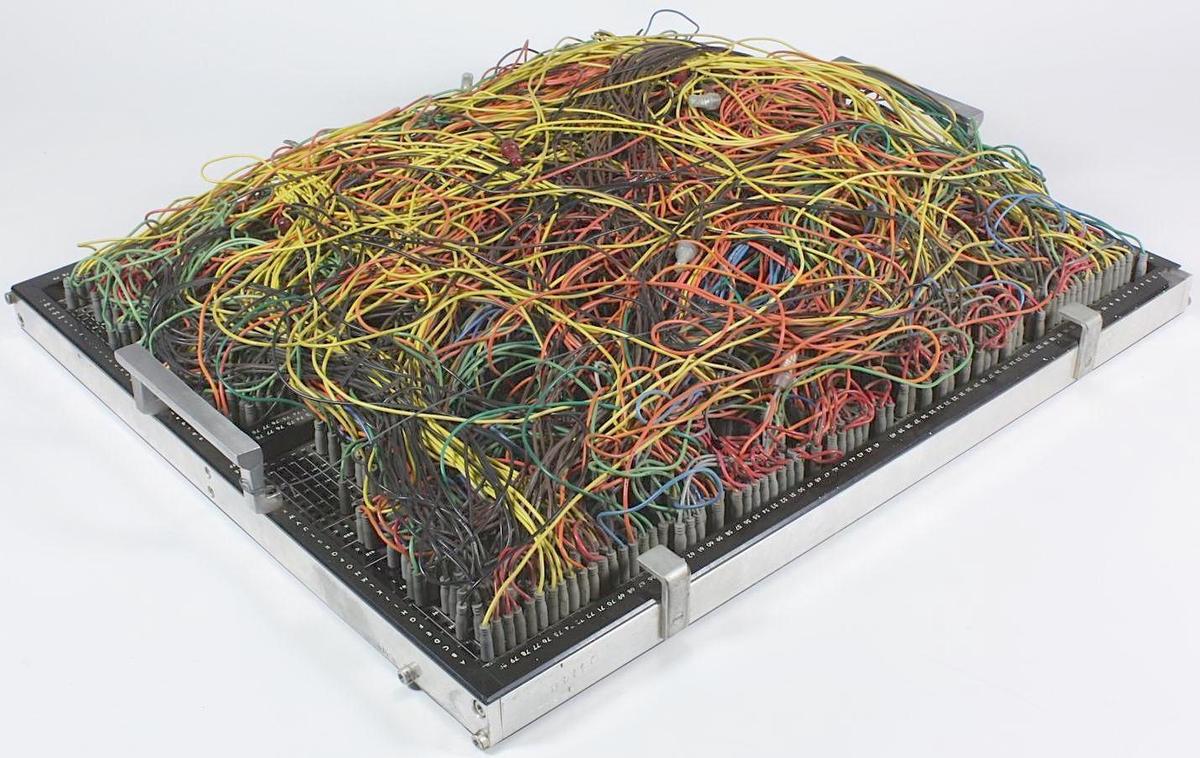

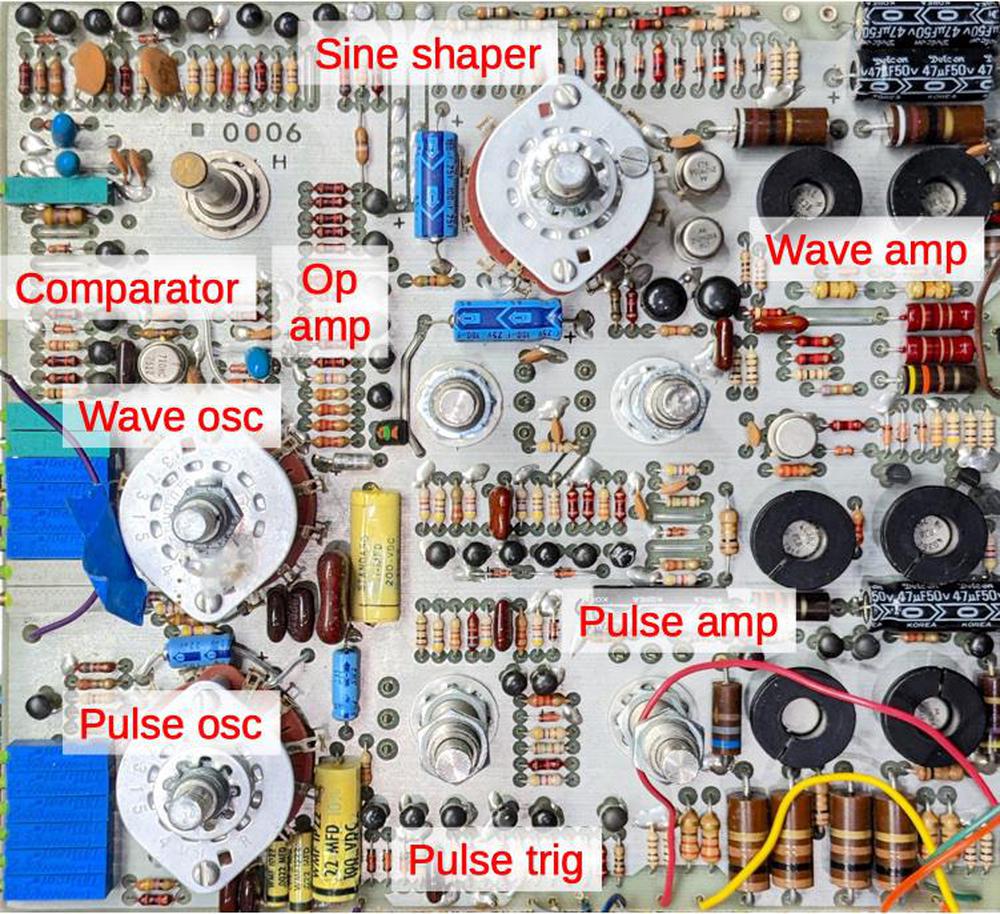

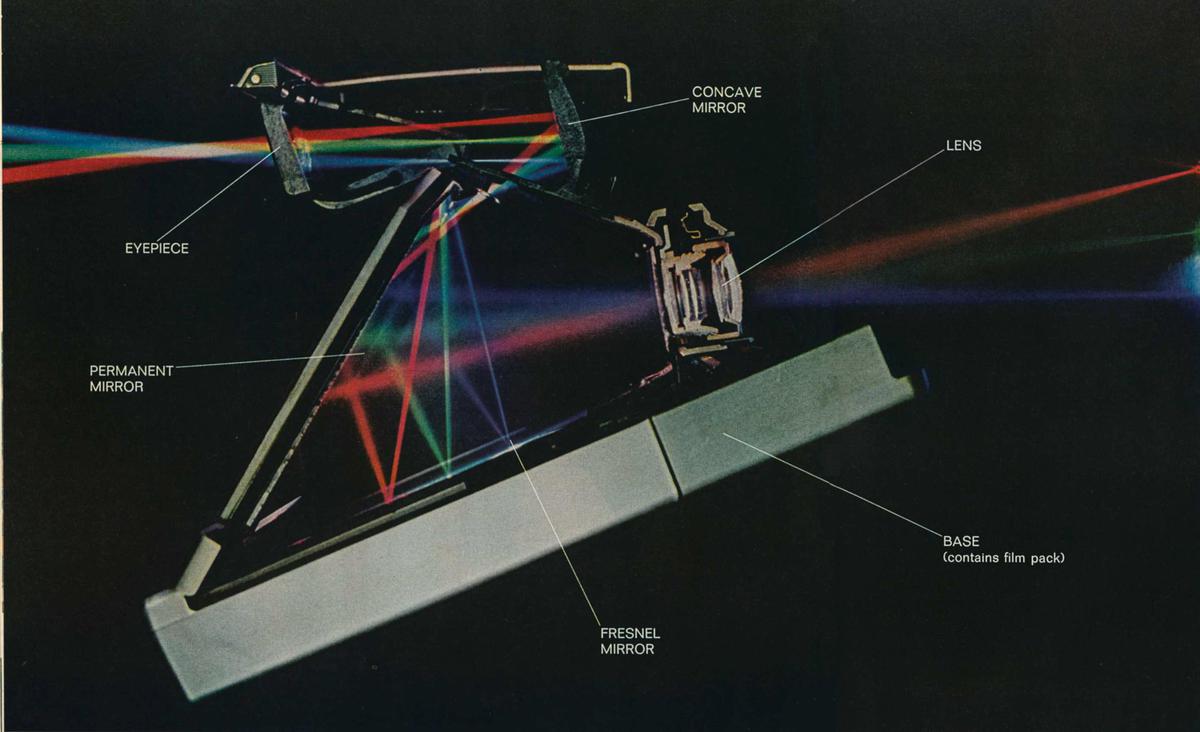

The most unusual feature of the Univac 1004 was that it was programmed by a plugboard (below) instead of a stored program. The system was programmed by plugging patch cords into a plugboard to indicate the desired action for each of the 31 program steps. While earlier electromechanical accounting machines used plugboards, they were pretty much obsolete by 1963, so I was a bit surprised to see plugboards still in use.

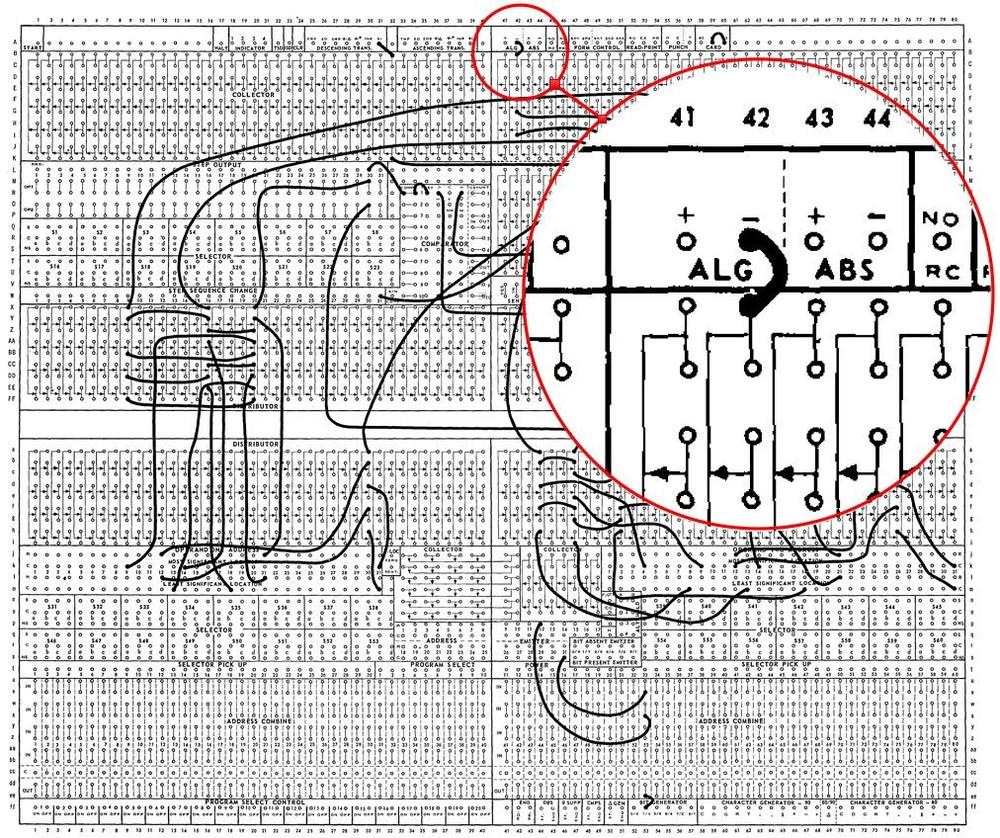

The computer's "program" consisted of 31 steps. The operations for each step were specified by plugging wires into the board. For instance, a data field could be moved from a punch card to memory, a value could be added or subtracted, or a line of output could be configured for the printer.5 The system even supported conditional branches. The diagram below shows the structure of the plugboard. The highlighted wire shows a subtraction operation, activated by the wire in the "algebraic minus" position.

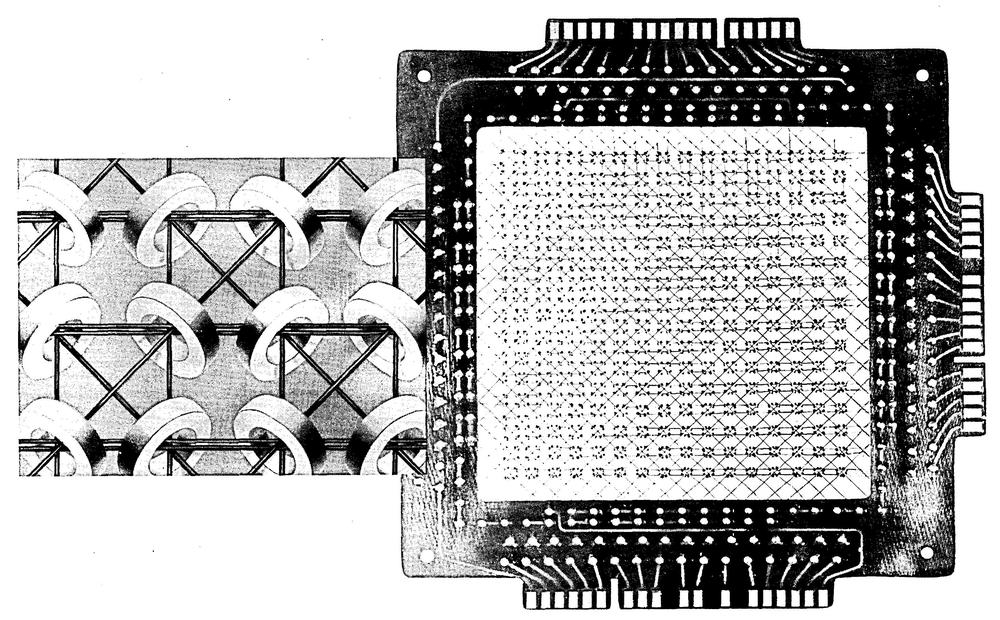

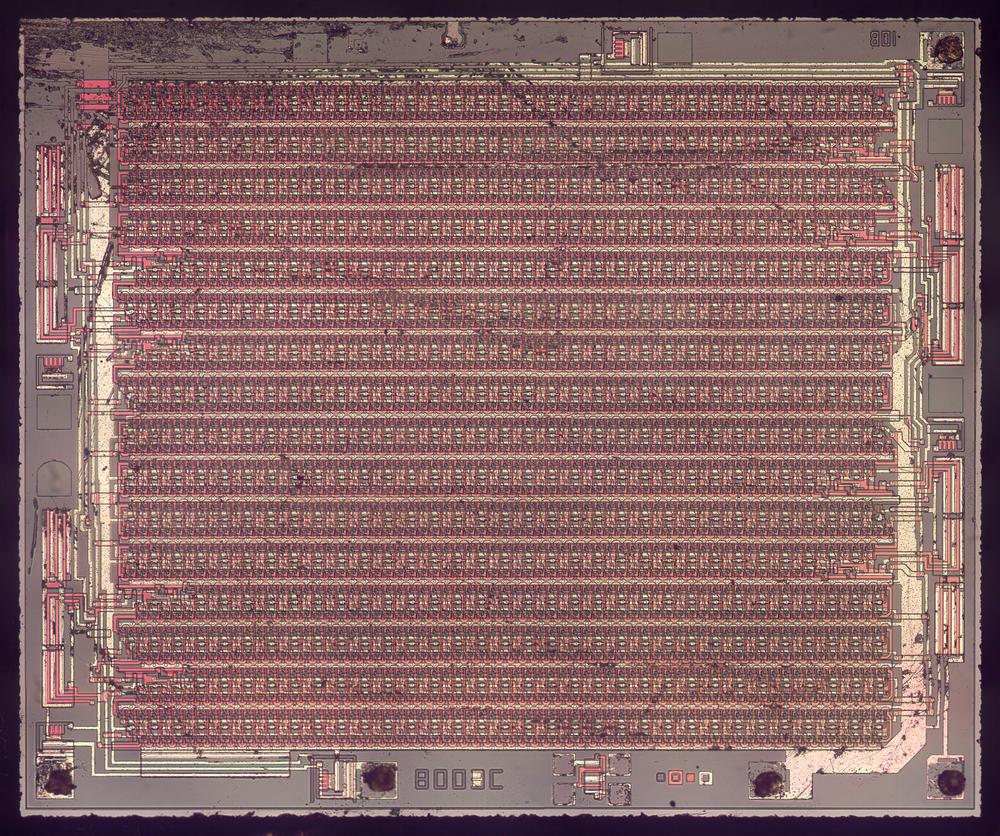

The computer had a small memory of 961 6-bit characters. Like most computers of the era, it used magnetic core memory, storing each bit by magnetizing a tiny ferrite ring. Note that since the computer was programmed through a wiring panel, none of the memory was used for program code.

While the Univac 1004 was primitive for its time compared to even a low-end business computer like the IBM 1401, it had a few advantages. First, it rented for $1900 a month, compared to $2500 a month for the IBM 1401 (about $18,000 vs $23,000 a month in current dollars). Second, the Univac computer was compact (by 1960s standards), weighing 2500 pounds. Finally, many customers found plugboard programming easier than programming with code, both because they were more familiar with it and because it is visual and direct.

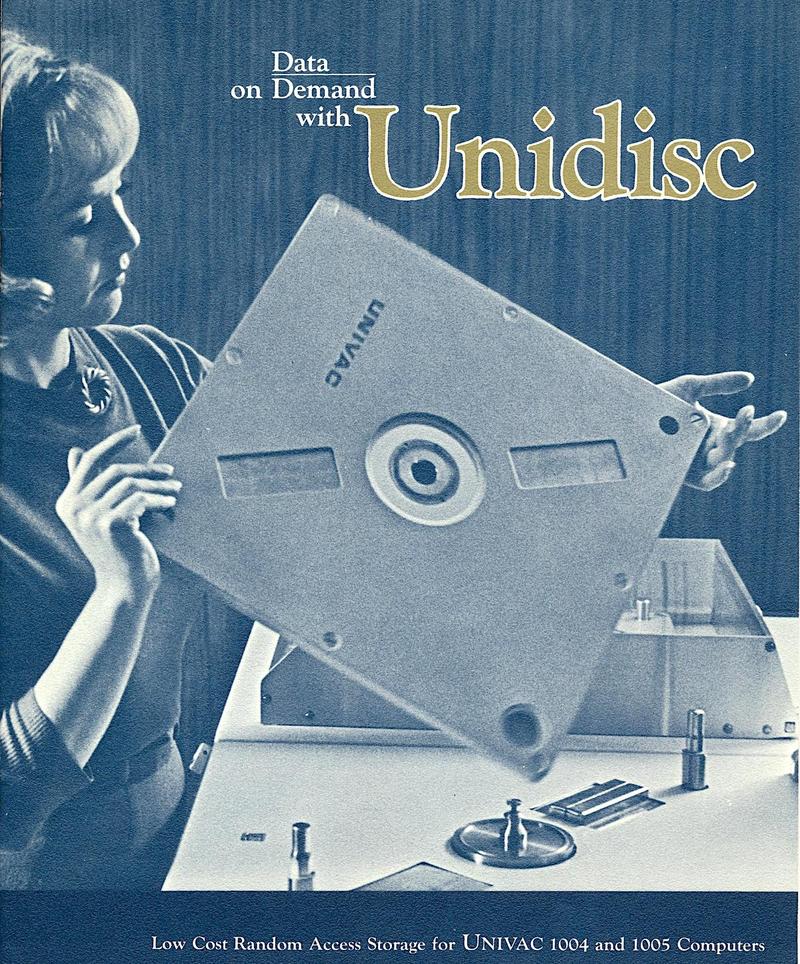

The Univac 1004 could be extended with peripherals such as tape drives, a card punch, or disk storage. The photo below shows the Unidisc cartridge, which held one million characters. Although it looks like an absurdly-large floppy disk, it was a removable hard disk.

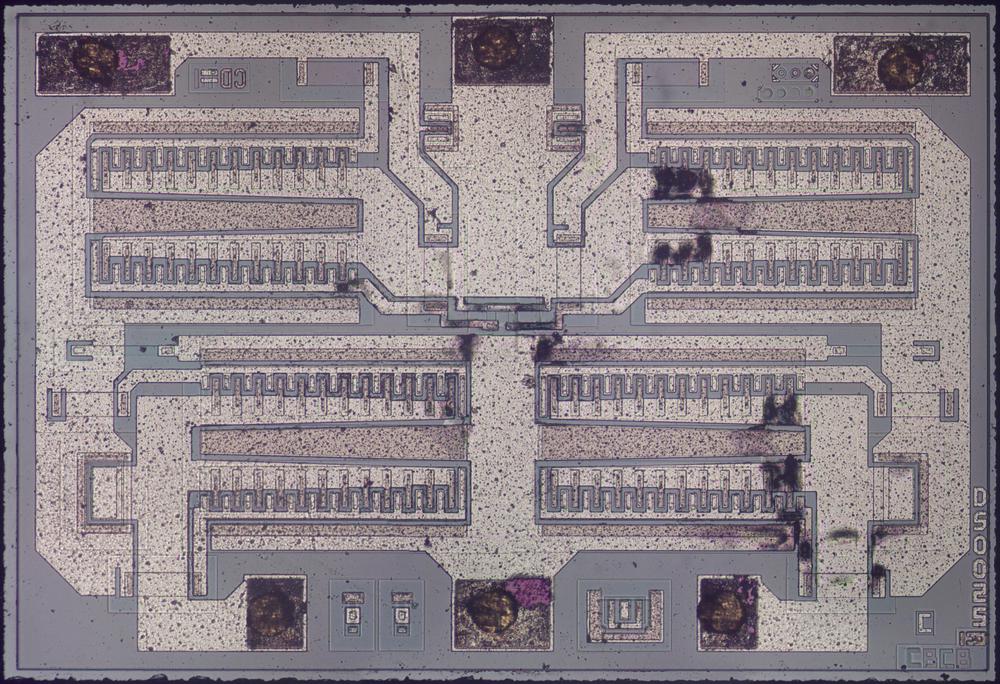

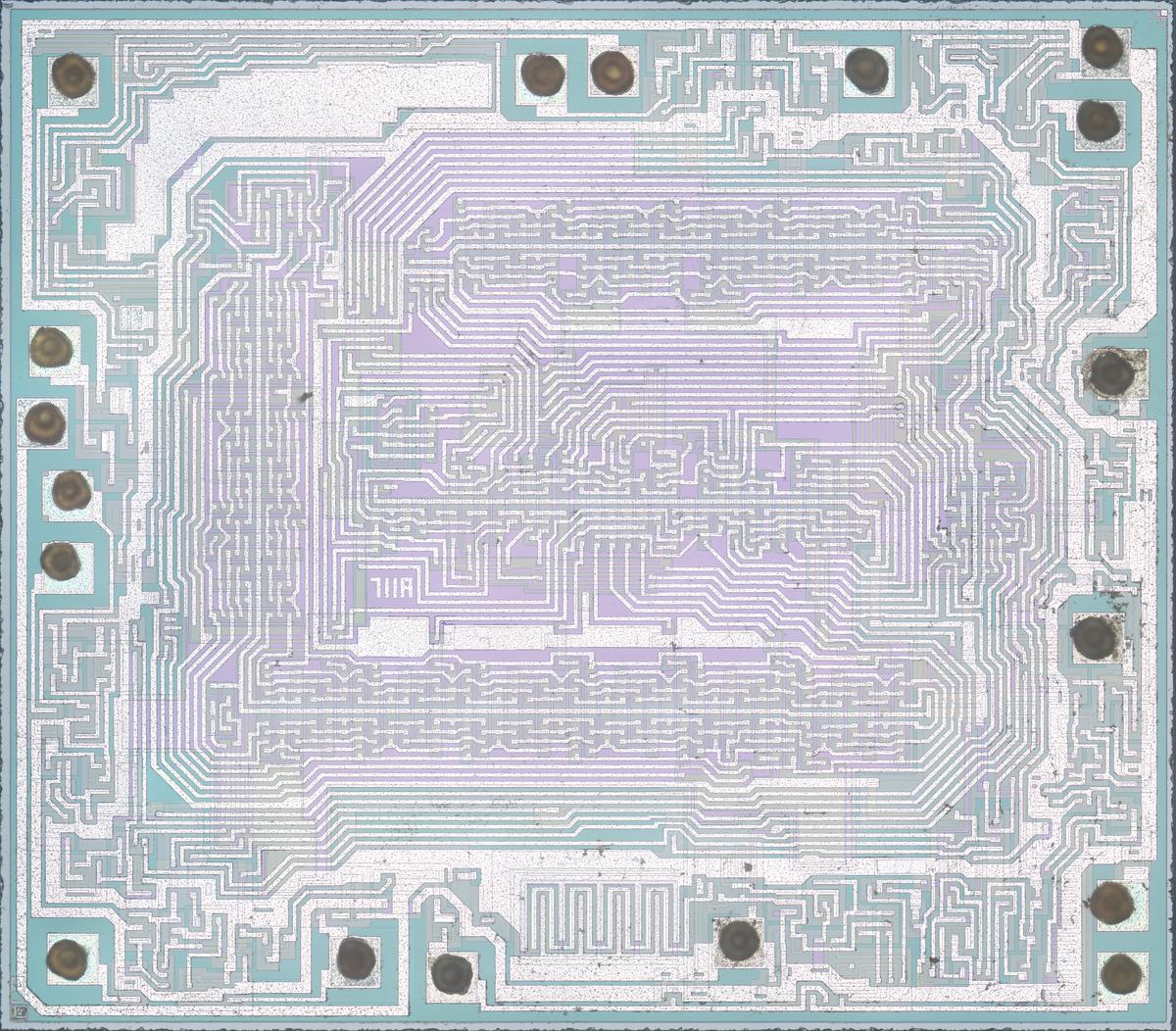

Reverse-engineering the board

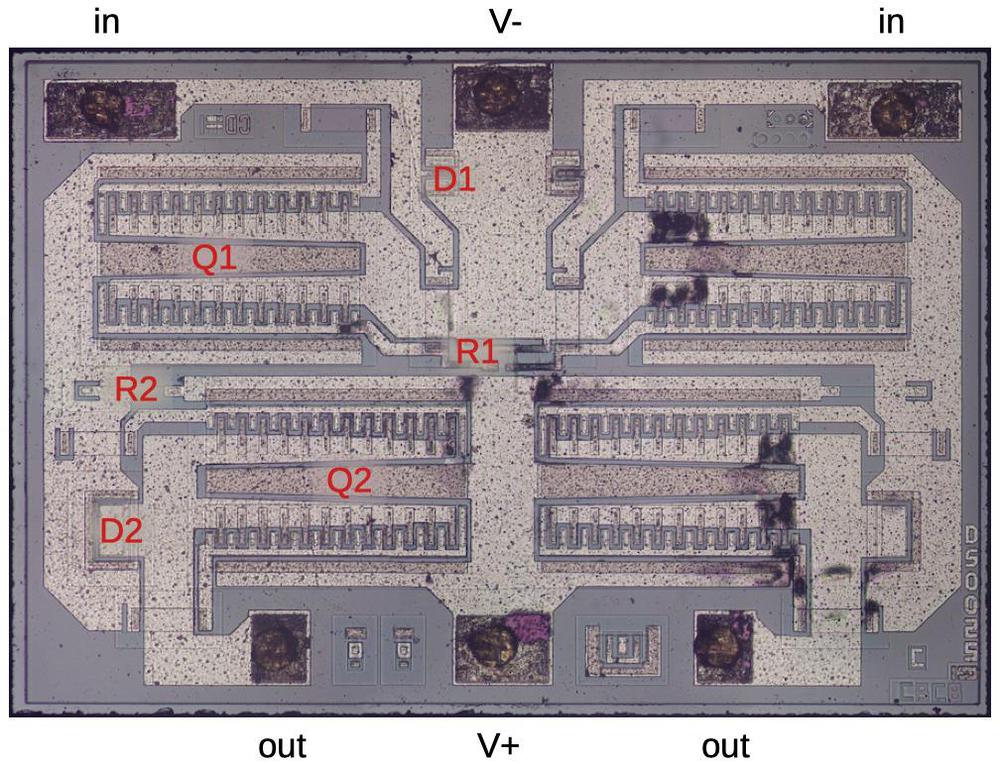

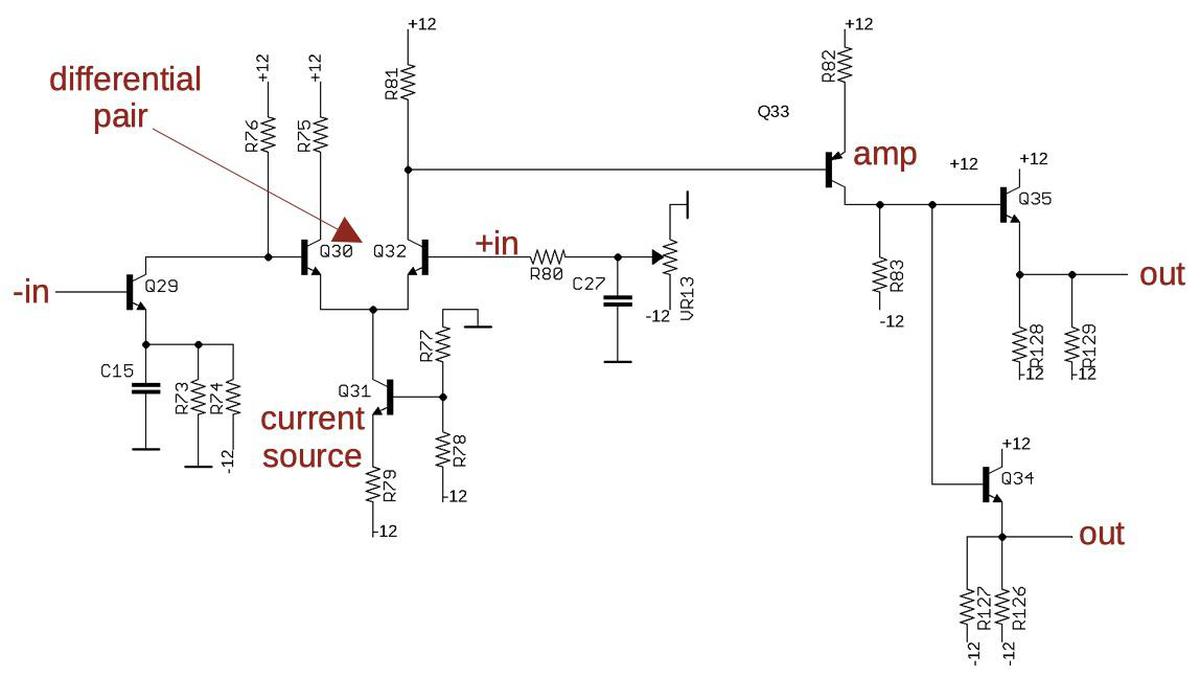

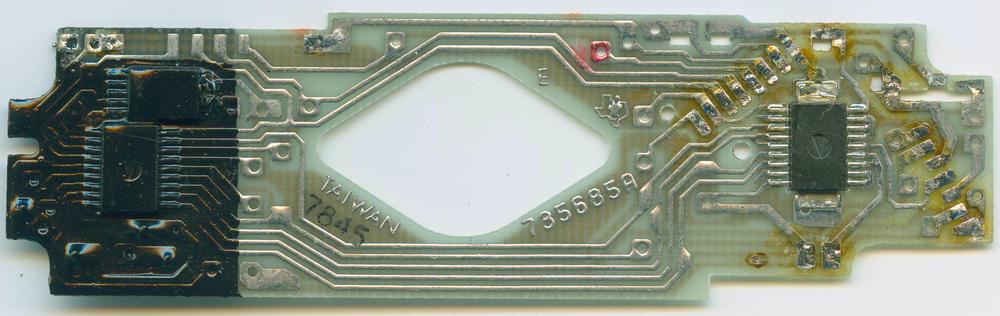

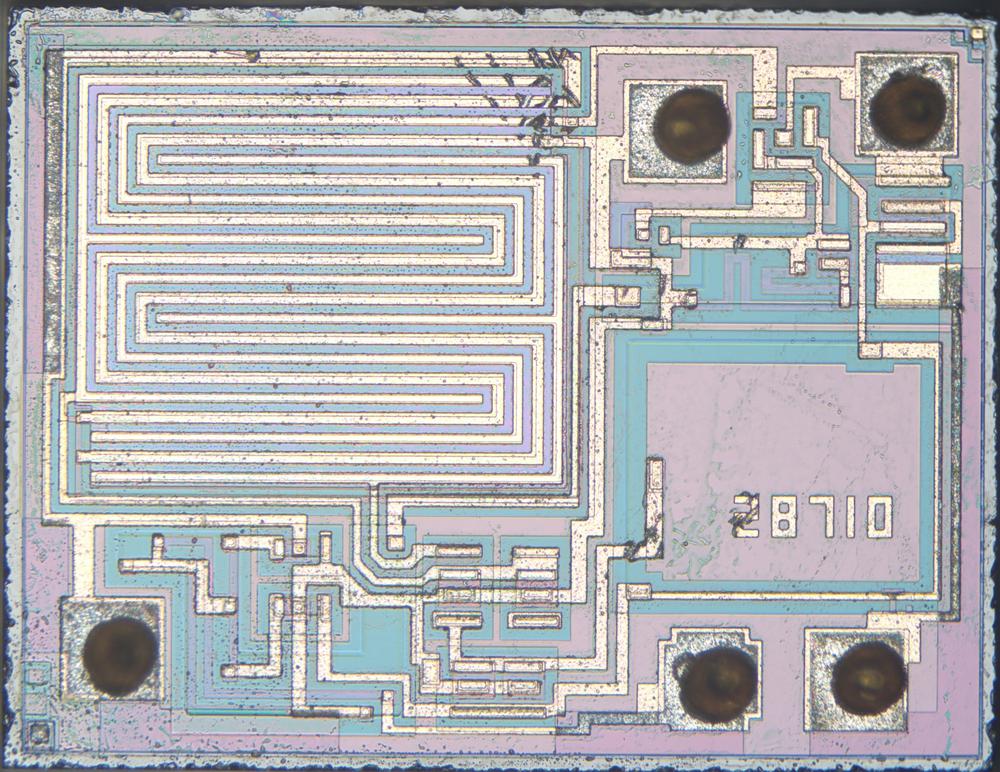

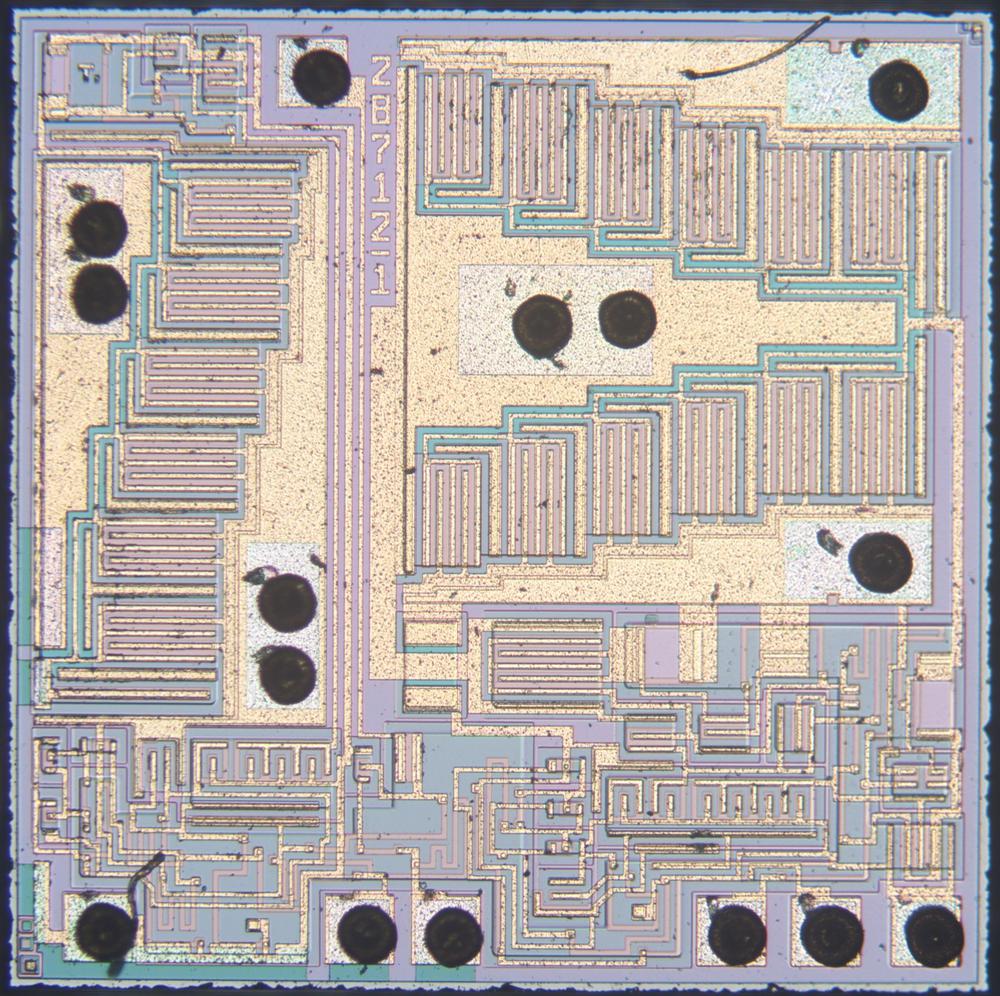

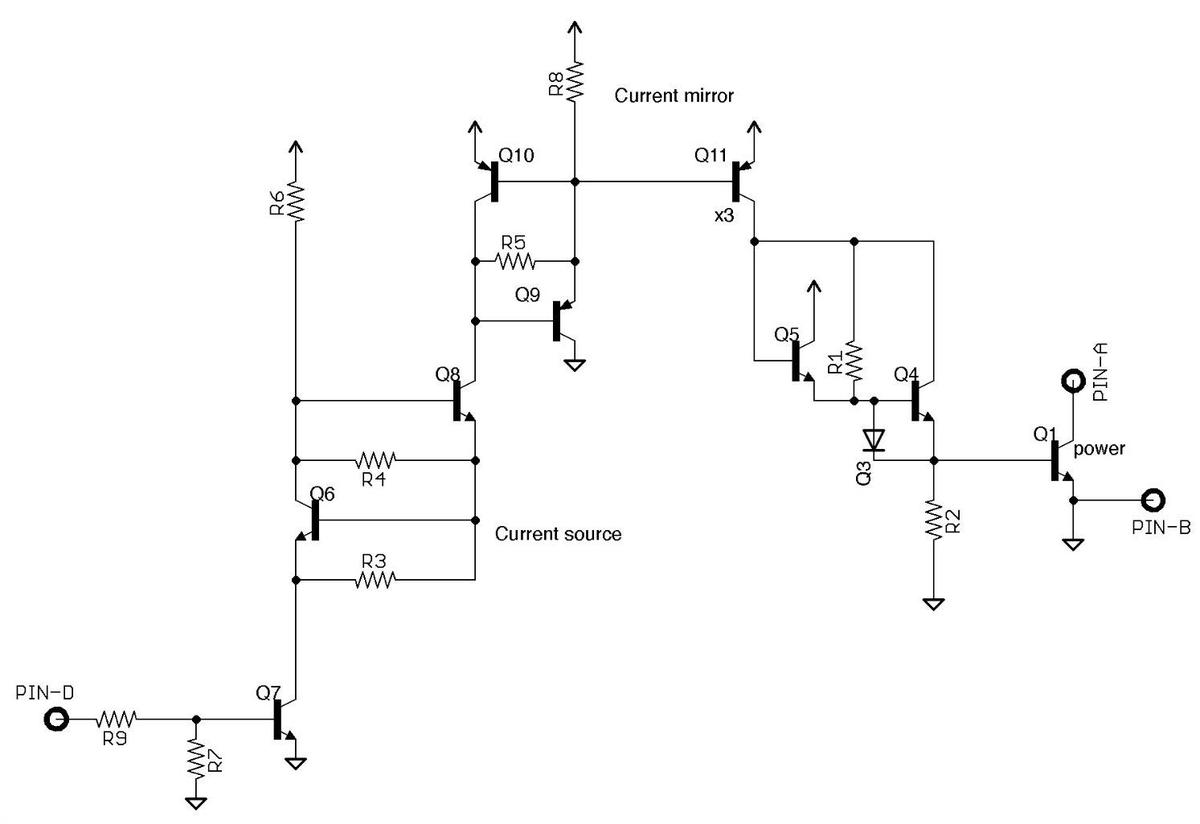

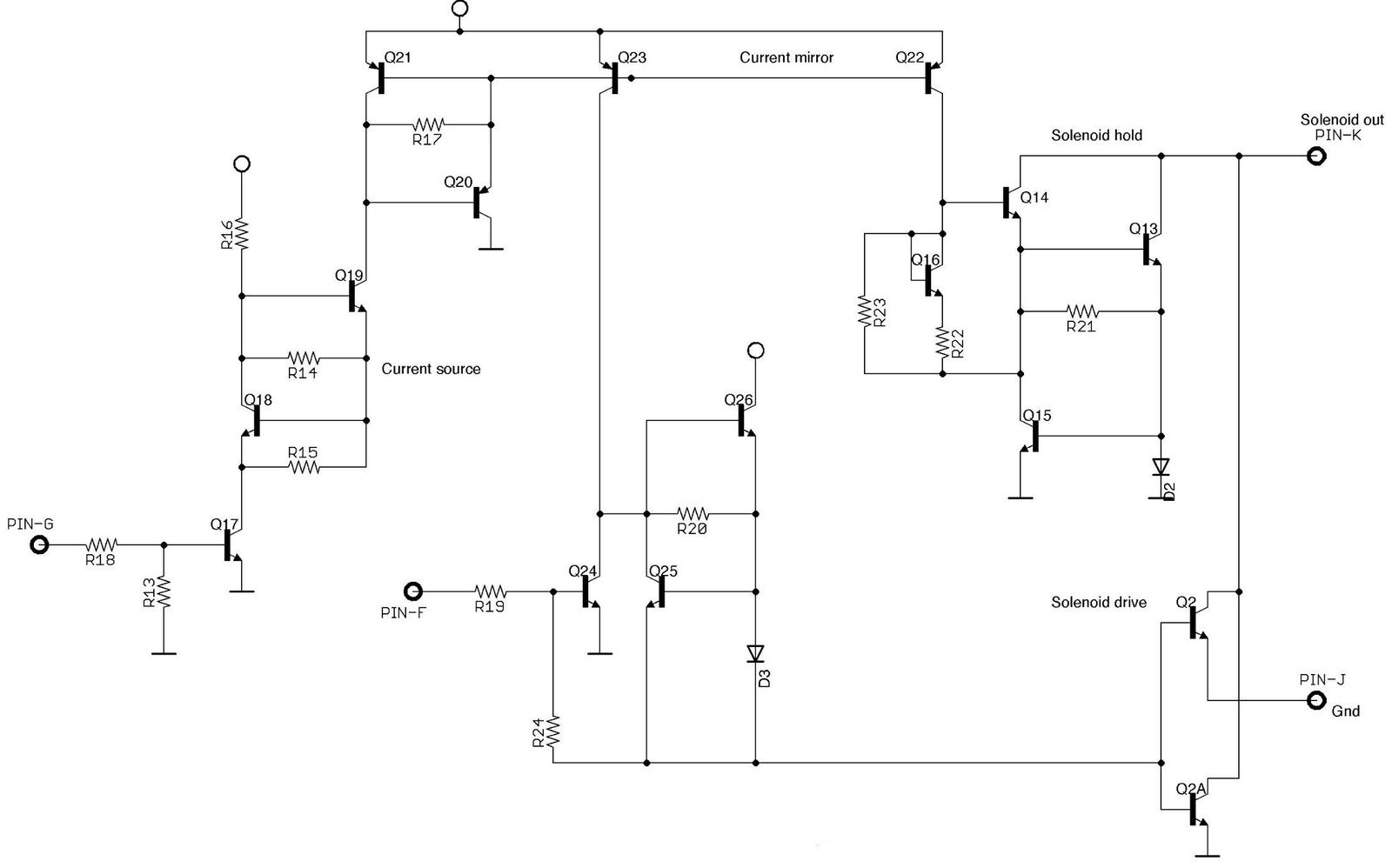

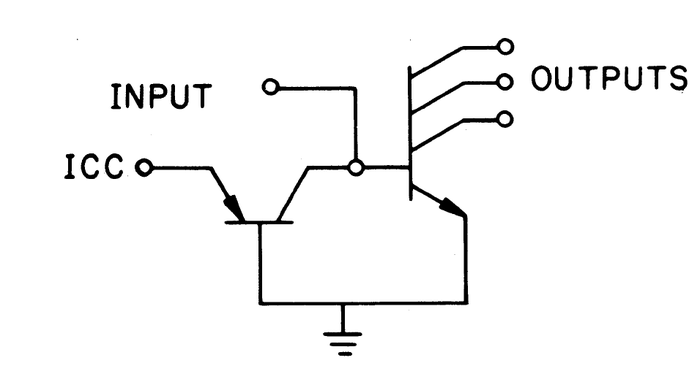

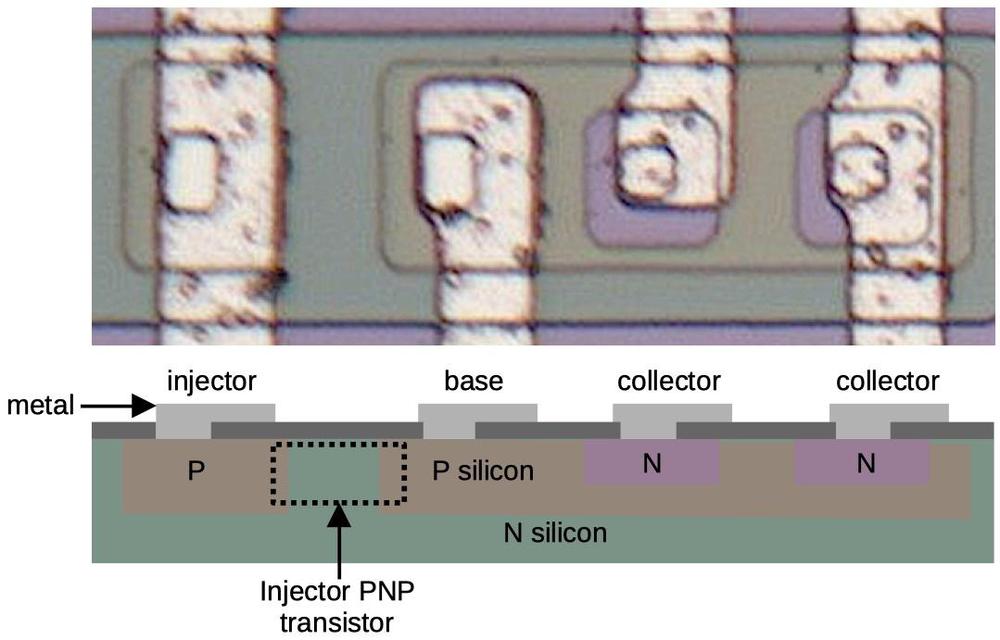

The function of the board wasn't immediately obvious and we had various theories of what it might do. To find out, I reverse-engineered the board by tracing out the circuitry.6 The board has 32 diodes, which seems like a lot, as well as resistors, transistors, and capacitors. The transistors are not silicon transistors, but germanium PNP transistors.

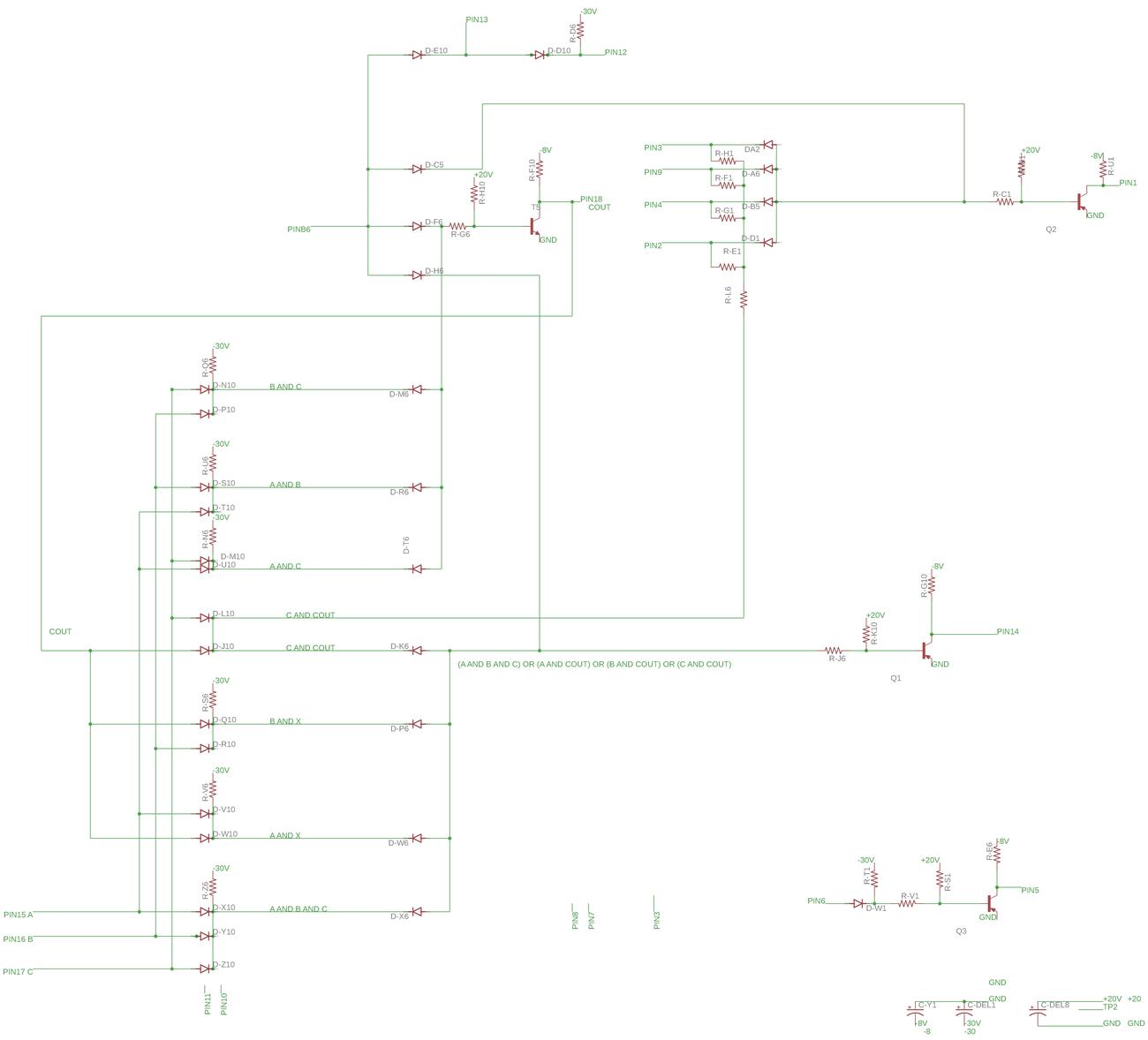

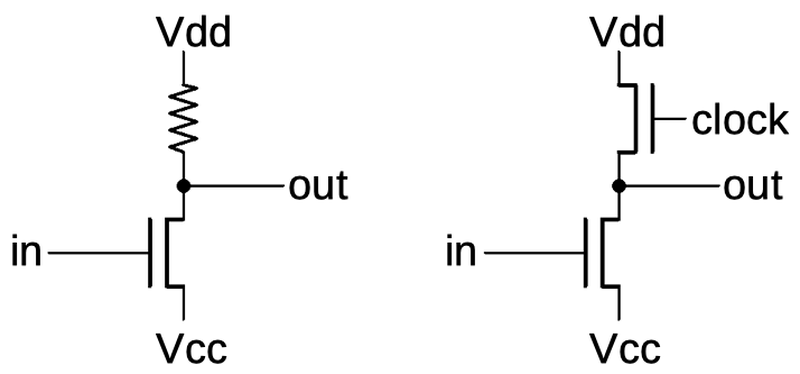

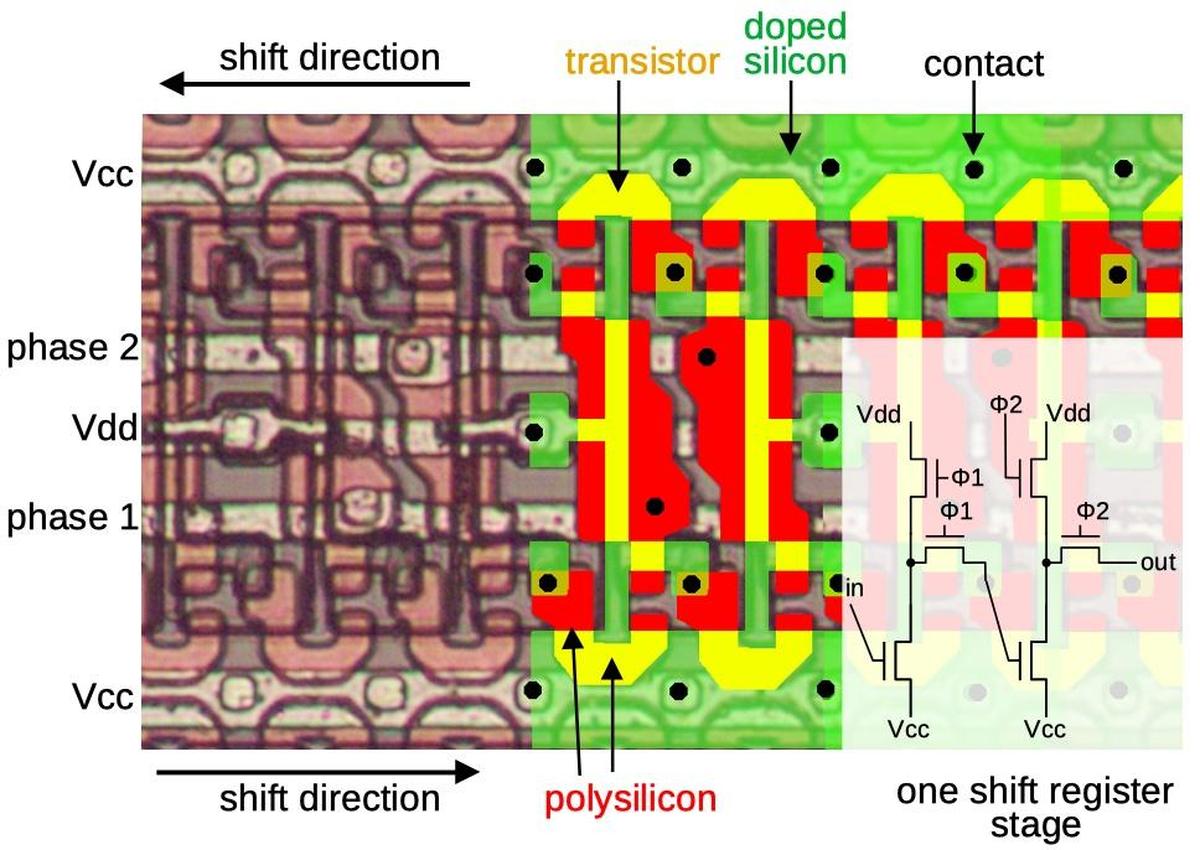

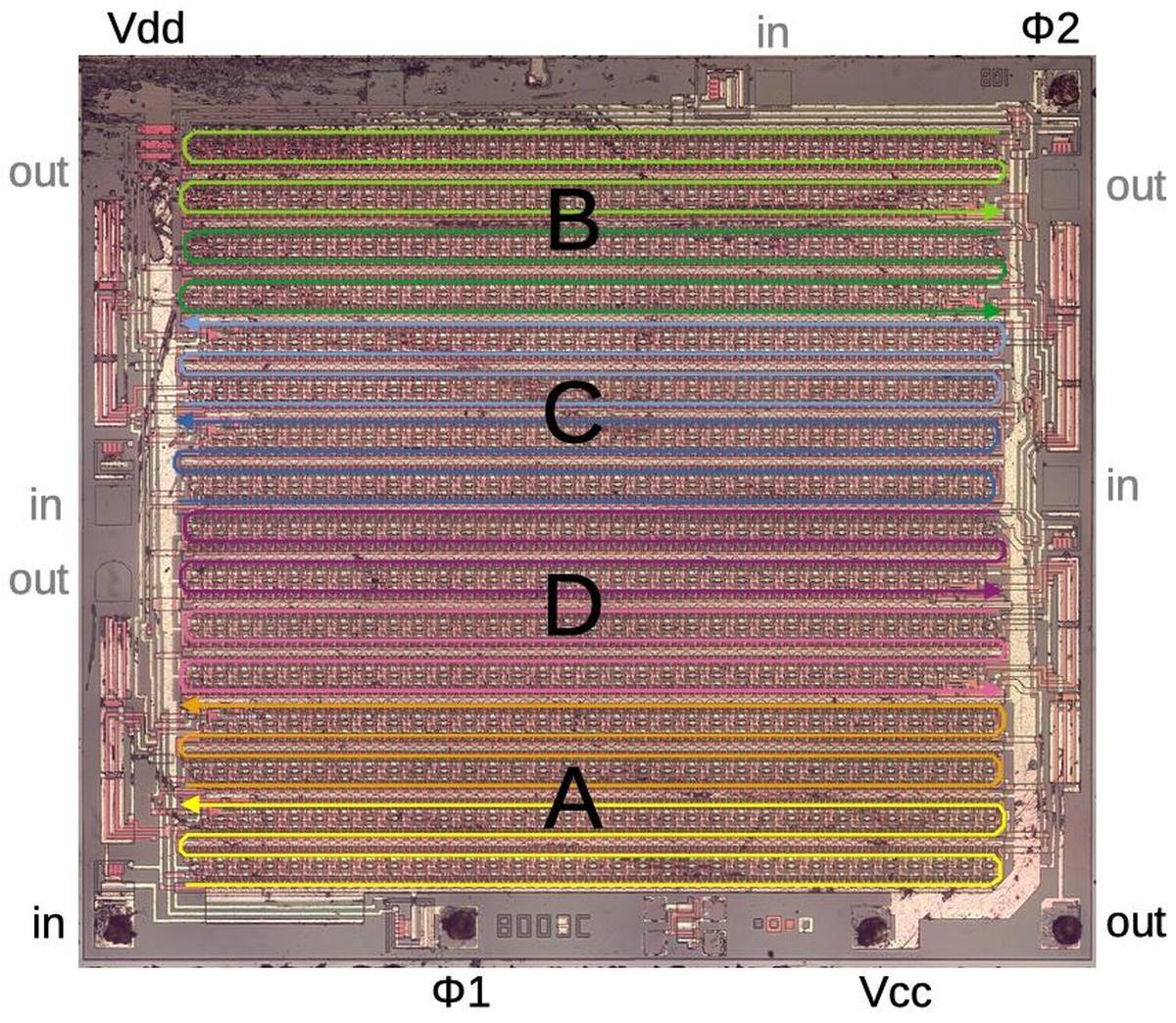

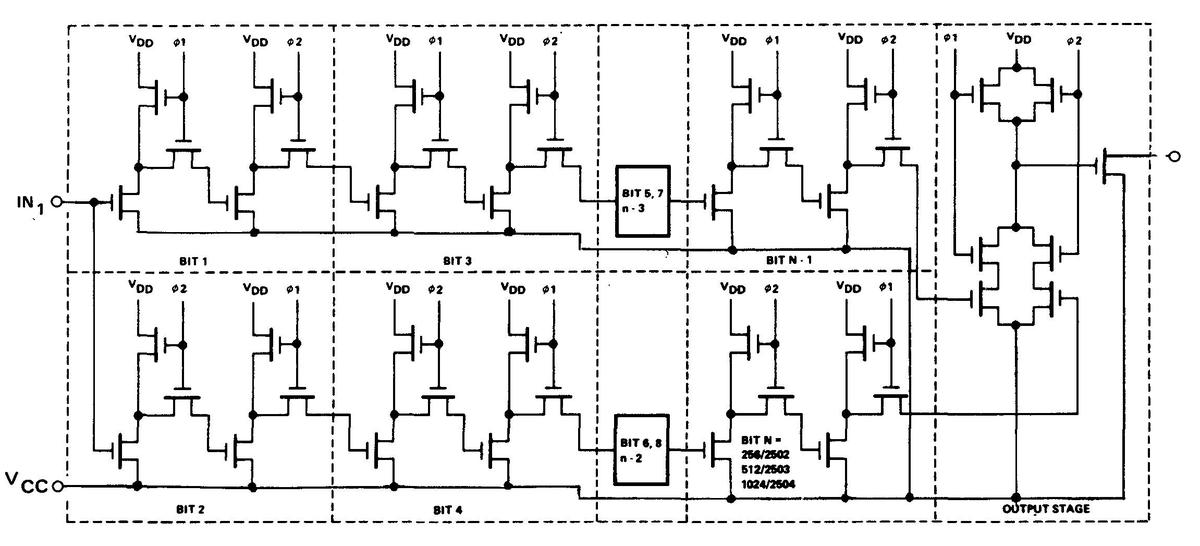

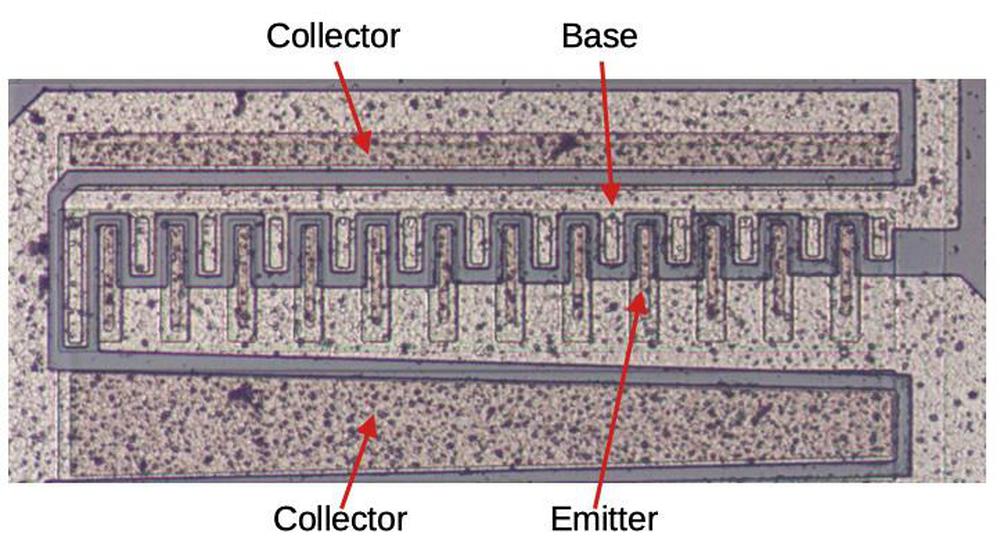

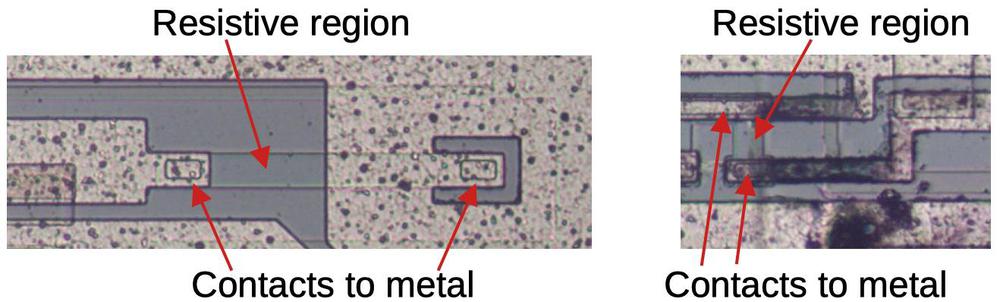

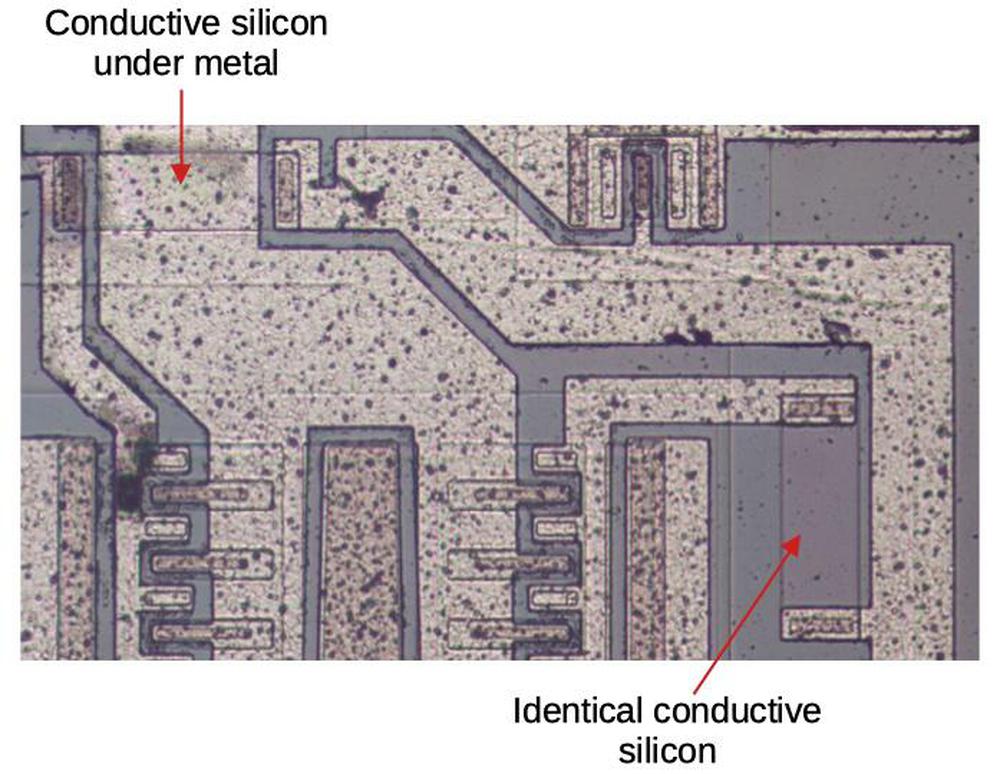

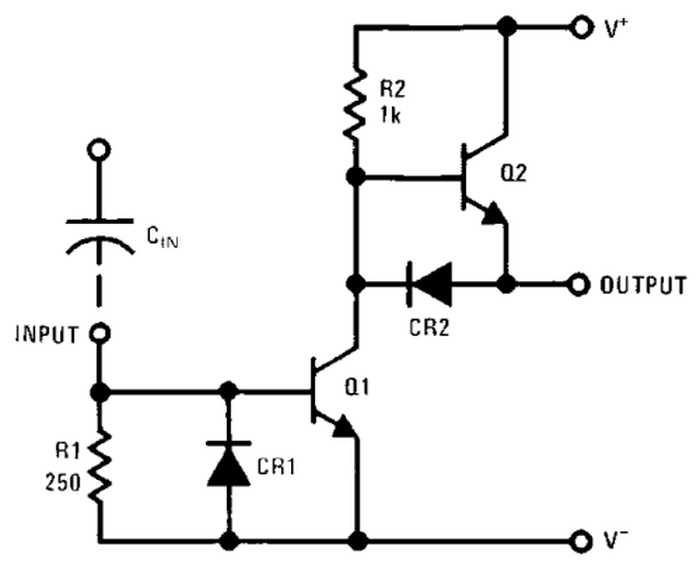

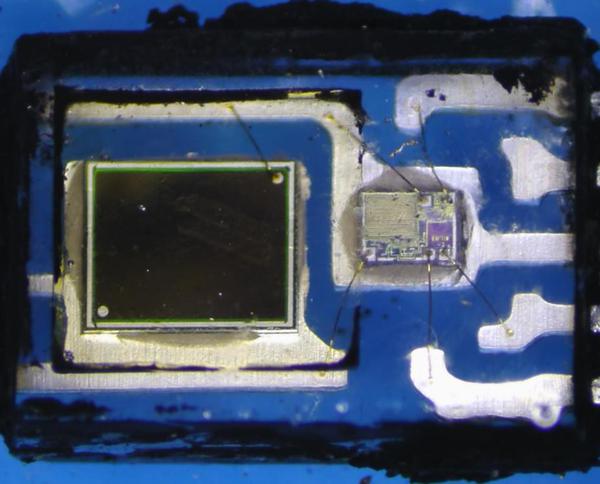

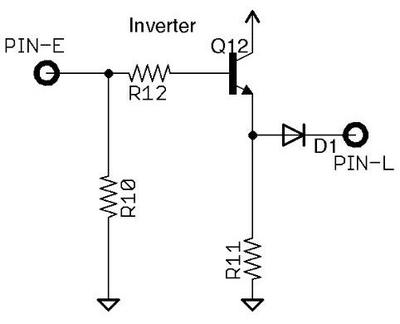

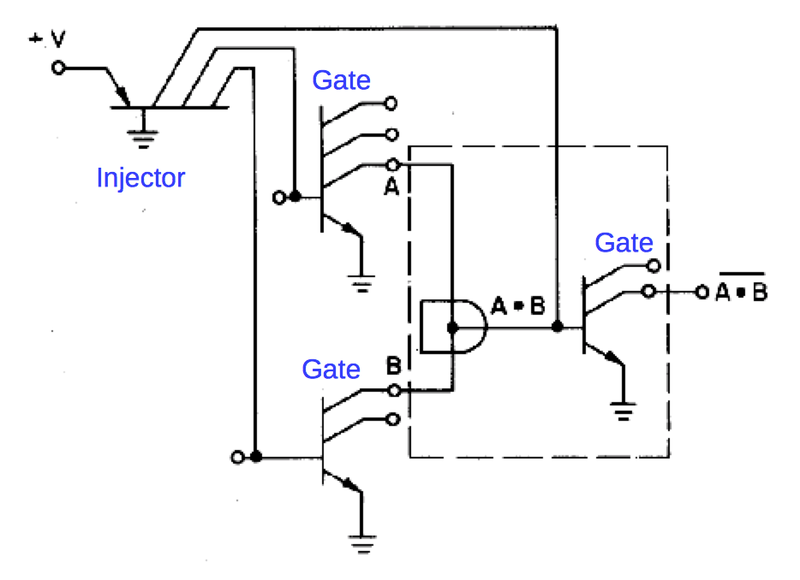

The board turned out to be a logic board implemented with AND-OR-INVERT logic.7 That is, various inputs are ANDed together, the AND results are then ORed together, and finally the result is inverted. The board is implemented with diode-transistor logic. One layer of diodes implements the AND gates and the second layer of diodes implements the OR gates. Finally, a transistor amplifies the result, inverting it in the process. Diode-transistor logic (DTL) performed better than earlier resistor-transistor logic (RTL), but was soon replaced by transistor-transistor logic.

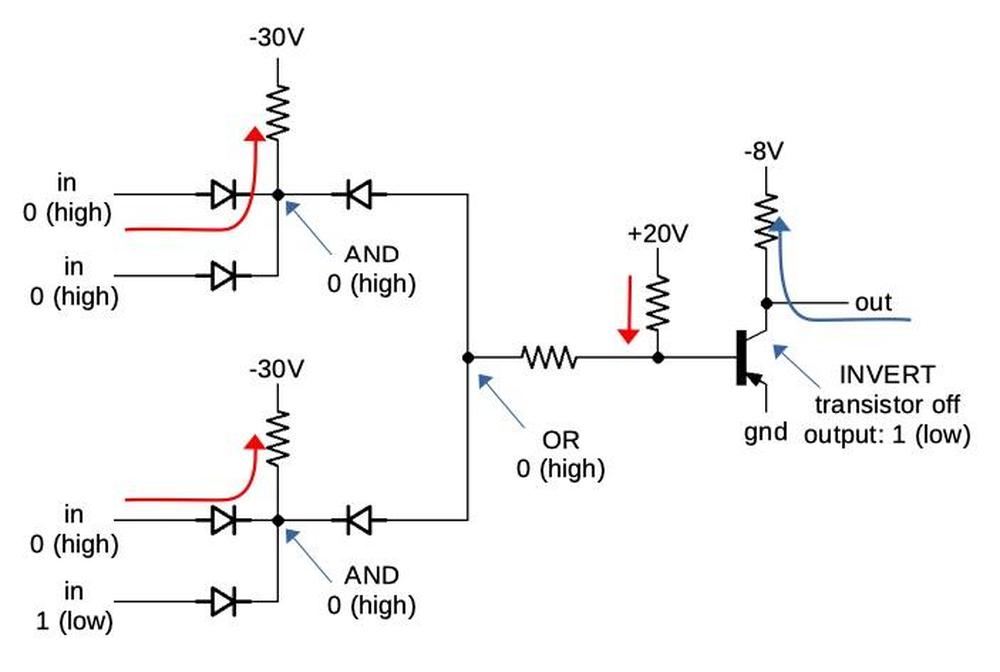

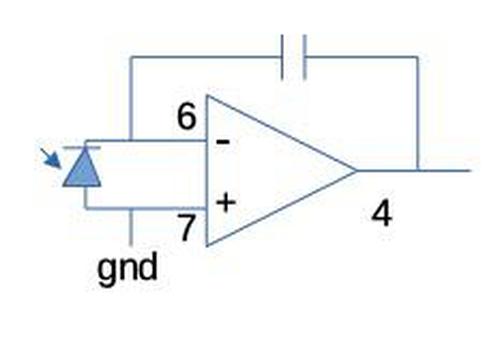

The diagram below explains how the AND-OR-INVERT logic was implemented. This circuit has four inputs: two AND gates that are then ORed together and inverted. (It's a bit confusing because the circuit uses active-low logic, so the voltage levels are all inverted.) If the AND gates all have a 0 (high) input, a diode in the first stage will conduct and pull the AND node high. This blocks the diodes in the second stage (which have the opposite orientation), so the OR node is also high. In the INVERT stage, the +20V resistor will pull the transistor's base high, which turns it off (since it is PNP). Finally, the -8V resistor will pull the output low (i.e. 1), providing the desired AND-OR-INVERT logic.

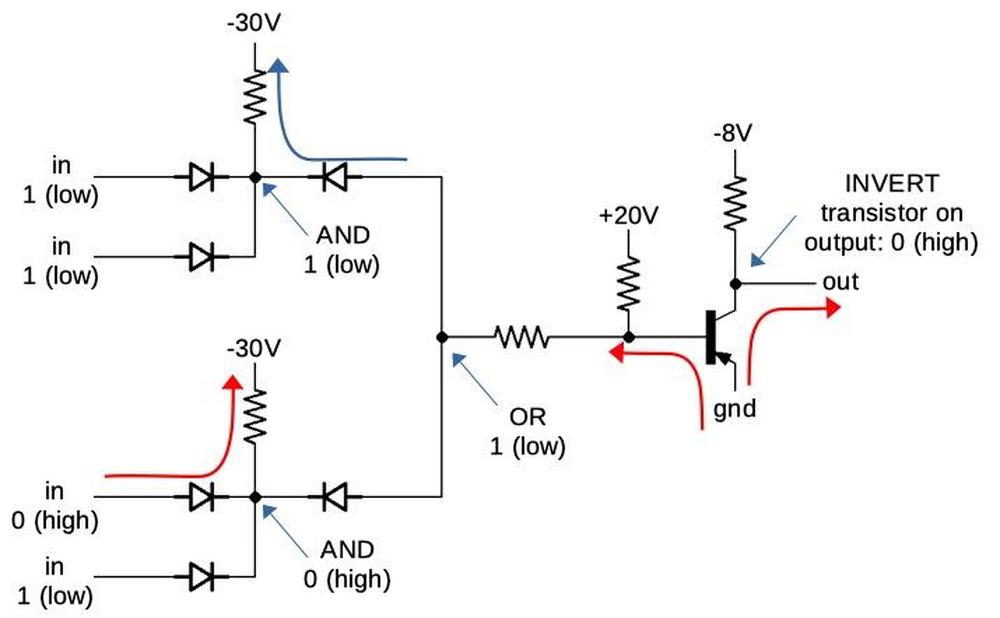

The diagram below shows that if the first AND gate's inputs are 1 (low), the first diodes are blocked, so the -30V resistor pulls the AND node low (1). Now the second-stage diode conducts, pulling the OR node low (1). This allows base current to flow through the PNP transistor, turning it on. This pulls the output high (0). (Note that ground is a high output compared to the low output of -8V.) The gates on the board have more inputs, but use the same principle.

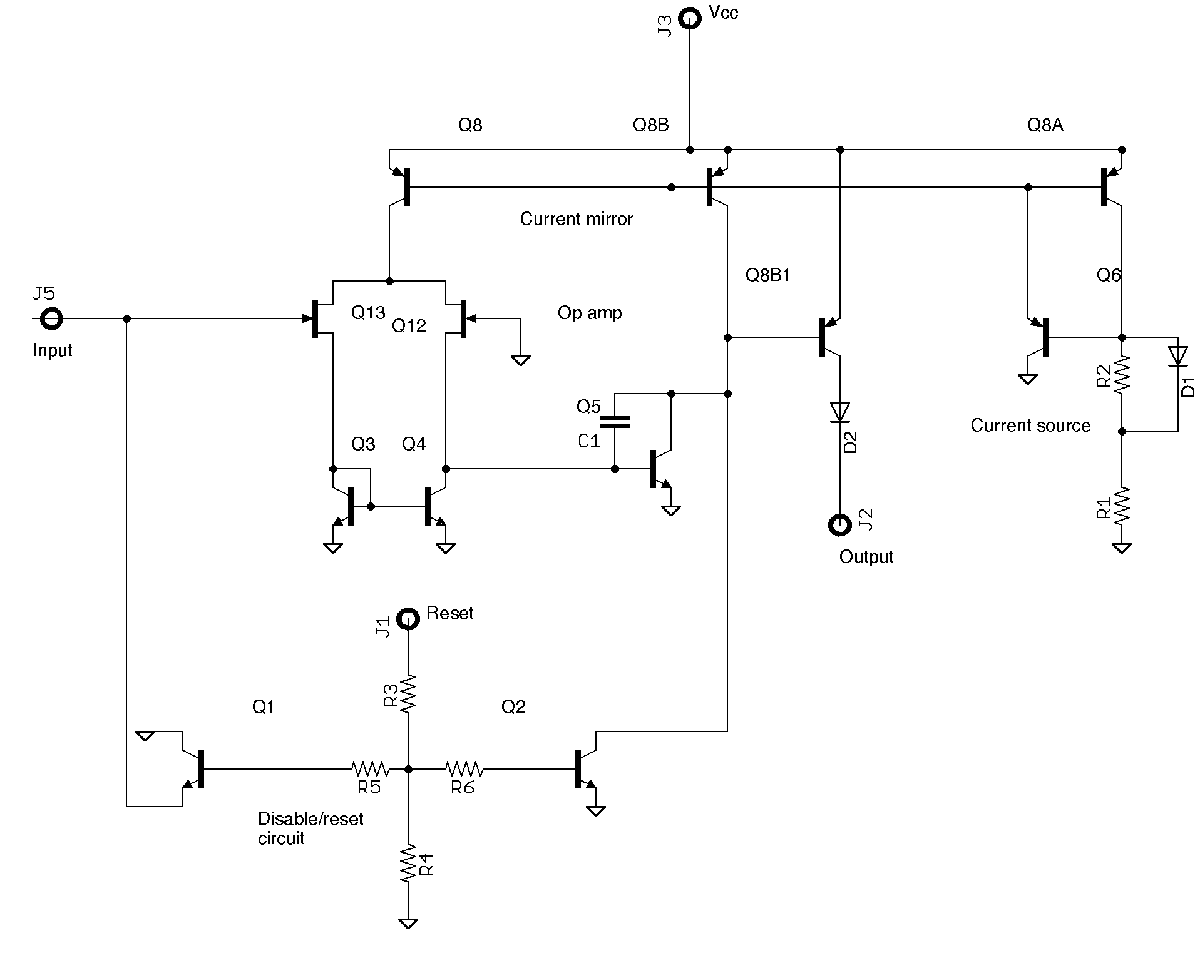

After tracing out the board's logic, I recognized that it implemented a full adder.8 That is, it adds two input bits along with a carry-in, producing a sum bit and a carry-out. By connecting four full-adders in series, a 4-bit value can be added, allowing one decimal digit to be added. Thus, the computer probably has four one-bit adder boards similar to this, along with circuitry to convert the output from binary to binary-coded decimal.10

The board has a few additional circuits along with the full adder circuit. It includes an inverter circuit. The board also has 4 inputs that are ANDed, subject to the carry value. Finally, the board also has a disable input that blocks the outputs.9 Without knowing more about the circuitry, I can't determine the role of these circuits.

Conclusion

The mystery circuit board turned out to be from the Univac 1004. Although this computer was produced in the 1960s, its technology occupies an interesting location between the electro-mechanical accounting machines of the 1940s and the electronic business computers of the late 1950s. The Univac computer used transistors and core memory, but it kept the earlier plugboard programming of the accounting machines, rather than moving to stored-program computing (introduced in 1948). Even though the Univac 1004 was technologically backward for 1963, businesses flocked to it, making it the second-most popular computer at the time with 3400 installations.4

This shows that progress isn't as linear as you might expect; "obsolete" technologies can continue to thrive long after the introduction of "superior" alternatives such as stored-program computing. Instead, new systems can still be developed with supposedly-obsolete technologies, depending on the tradeoffs involved.

I announce my latest blog posts on Twitter, so follow me @kenshirriff. I also have an RSS feed.

Notes and references

-

The Computer History Museum links to a similar board. ↩

-

The photo below compares the Univac board to a smaller IBM SMS board.

Comparison with an IBM SMS card. -

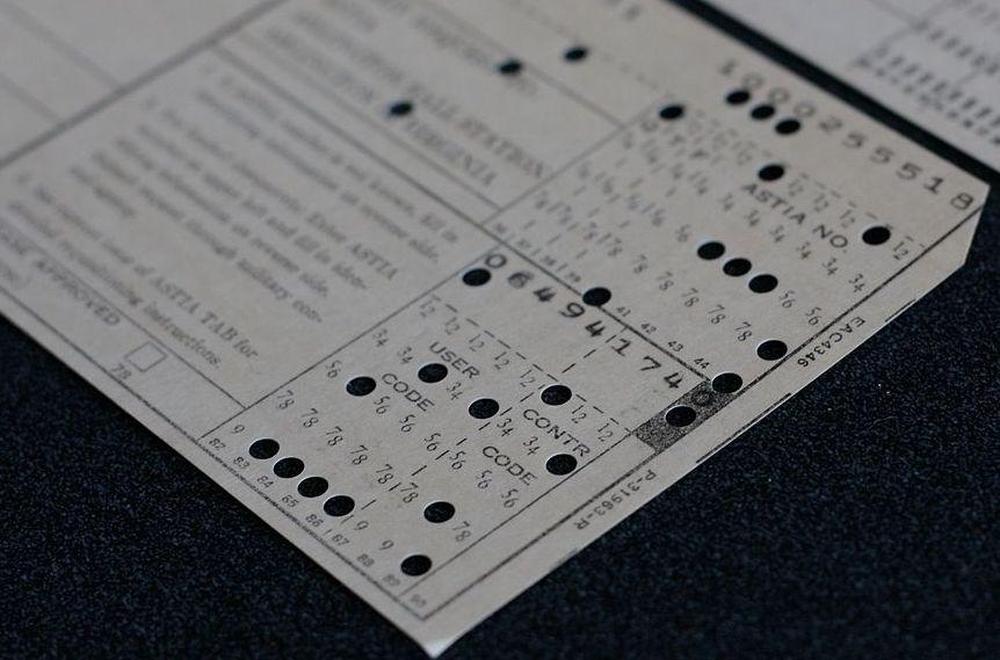

The Univac 1004 computer came in two versions. The "80" read standard IBM 80-column punch cards. The "90" read Univac's 90-column cards (details), which held 90 characters per card instead of 80. The 90-column card was introduced in 1930 by Remington Rand. It had round holes instead of IBM's rectangular holes. The card stored two characters per column by using a denser, binary code. Despite the superior capacity of the 90-column card, IBM's 80-column cards dominated the market. (Even IBM couldn't displace the 80-column card, although they tried with the 96-column card that they introduced in 1969.)

A 90-column punch card. From Marcin Wichary, (CC BY 2.0). -

Robert Garner discusses the Univac 1004 briefly in his article on Early Popular Computers. More information is in the 1964 BRL report as well as on Bitsavers. A related board from the Univac 1040/1050 is described here. ↩↩

-

The plugboard supported conditionals and looping, so I think the system was Turing-complete, although you couldn't do a lot in 31 programming steps. You could implement multiplication or division with a short shift and add (or subtract) loop. ↩

-

To reverse-engineer the board, I took photos of both sides, flipped the image of the back in GIMP so the two sides were aligned visually, arranged the components on a schematic in EAGLE, and connected the components to match the circuit board. Then I moved the components around until the layout made sense.

The underside of the circuit board.The back of the circuit board is shown above. Note that the edge connectors are completely different on the two sides of the board.

-

AND-OR-INVERT logic was also used in the IBM System/360 computers, although it was built from hybrid SLT modules instead of discrete components. ↩

-

I suspected the board was an adder when I saw that it had three inputs and was combining them symmetrically. The full adder is implemented in AND-OR-INVERT logic as follows. If the two bits are A and B and the carry-in is CIN, then a carry-out (COUT) is generated if at least two input bits are set. This is computed by the AND-OR logic "(A and B) or (A and CIN) or (B and CIN)". The sum bit is set if there is a single 1 input or three 1 inputs. The sum bit was computed by "(A and not COUT) or (B and not COUT) or (CIN and not COUT) or (A and B and CIN)" As a result of the AND-OR-INVERT circuit, the output is inverted. The inverter circuit on the board was probably used to un-invert it. ↩

-

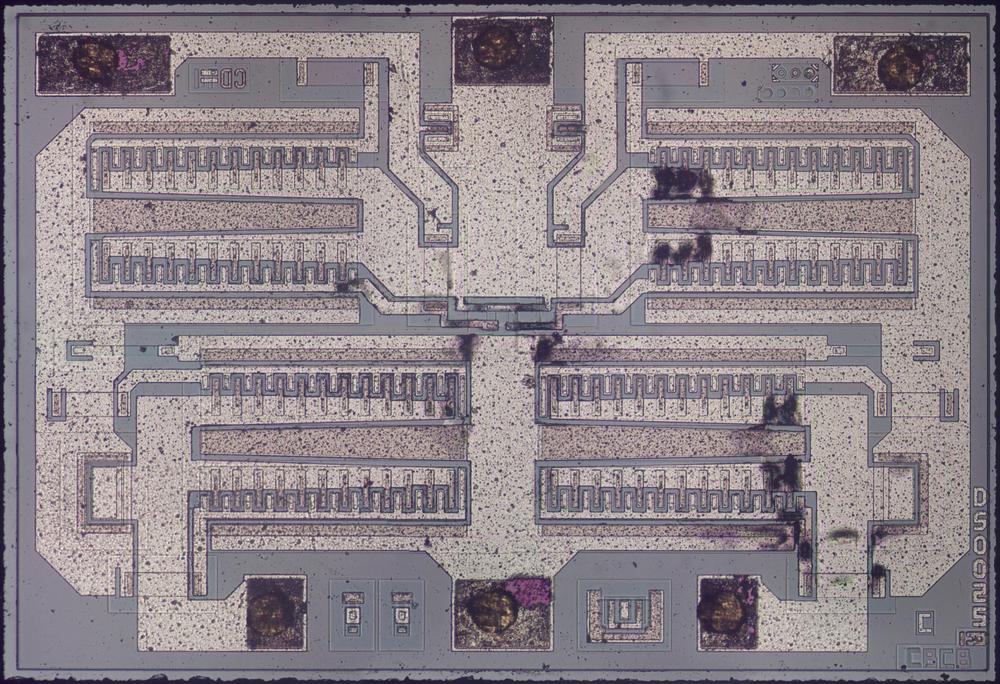

The full reverse-engineered schematic is below.

Reverse-engineered schematic of the board. Click for a larger version. -

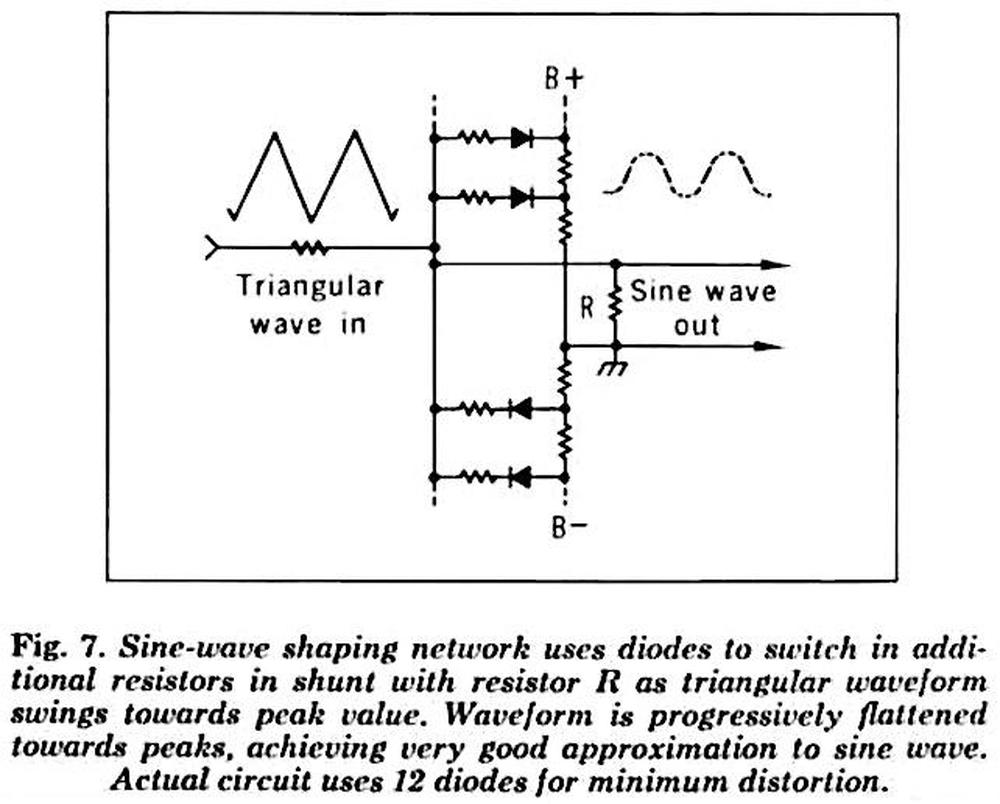

The computer uses excess-three encoding for digits, adding 3 to the value before converting to binary. For example, 6 is represented as binary 1001. The advantage of this encoding is that flipping the bits yields the 9's-complement decimal value, simplifying subtraction. For example, flipping the bits of 6 yields binary 0110, which is 3 in excess-3 notation. Excess-3 representation also handles carries correctly; if you add two numbers that sum to 10, the excess-3 values will sum to 16, causing a binary carry. To convert the sum to excess-3, The value 3 must be added (if a carry) or subtracted (if no carry).

To see how addition works with excess-3, 2 + 4 in excess-3 is binary 0101 + 0111 = 1100. Subtracting 3 yields 1001, which is 6 in excess-3. But 2 + 9 is binary 0101 + 1100 = 10001, generating a carry out of the 4 bit value. Adding 3 yields 0100, which is 1 in excess-3. Considering the carry-out, this is the desired result of 11. ↩