I've been studying the guidance computer from a Titan II nuclear missile. This compact computer was used in the 1970s to guide a Titan II nuclear missile towards its target or send a Titan IIIC rocket into the proper orbit. The computer worked in conjunction with an Inertial Measurement Unit (IMU), a system of gyroscopes and accelerometers that tracked the rocket's position and velocity.1

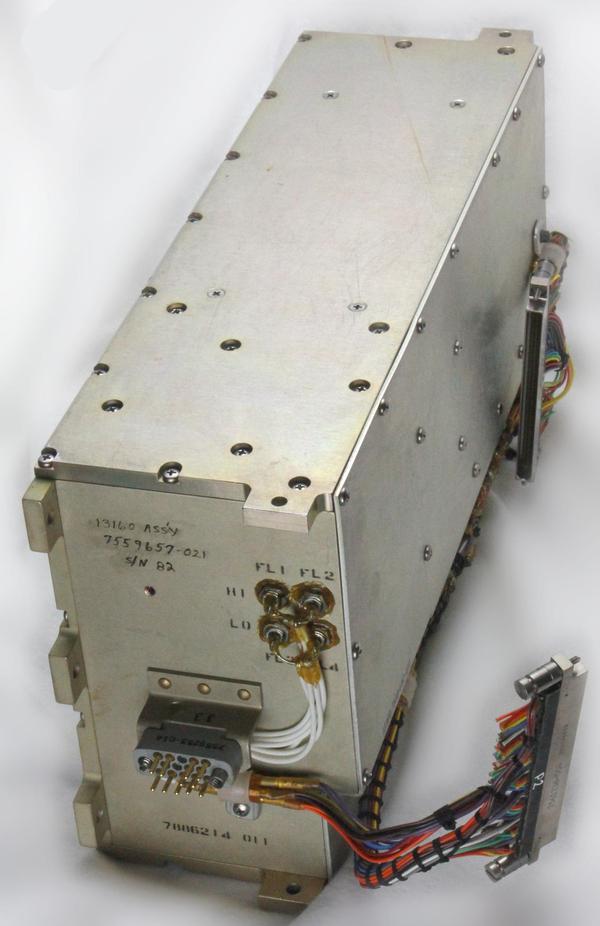

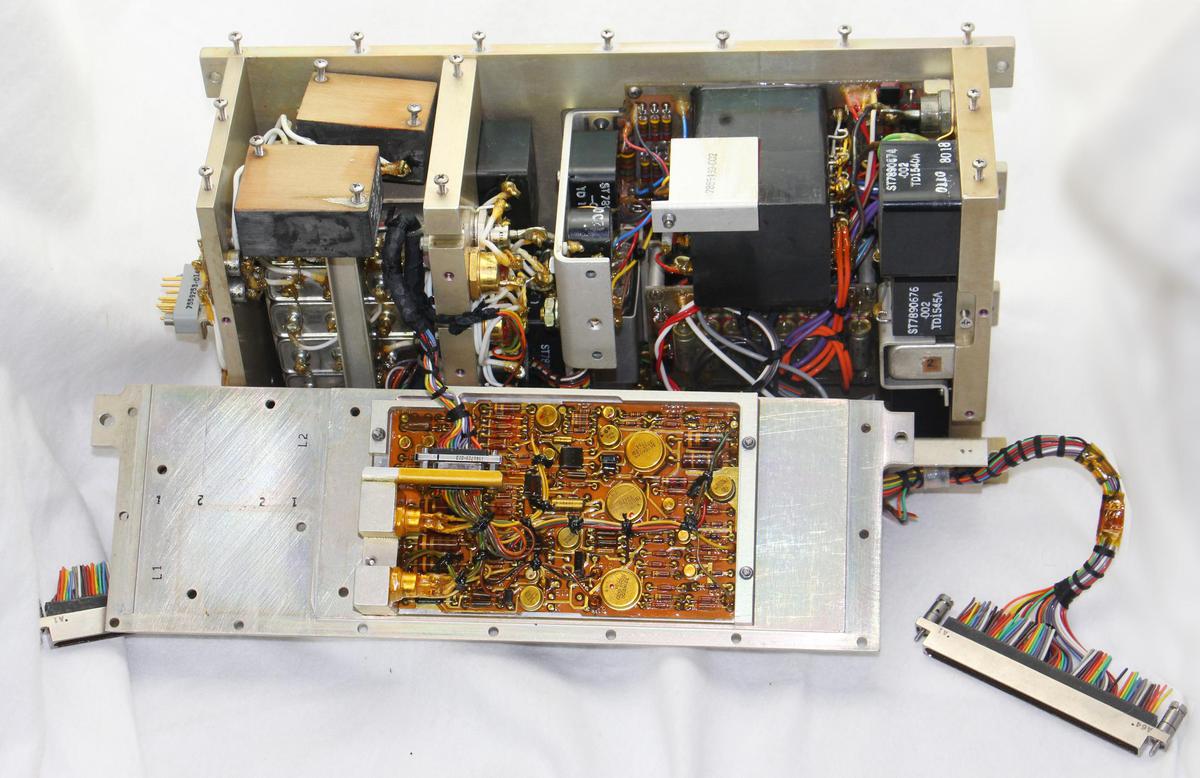

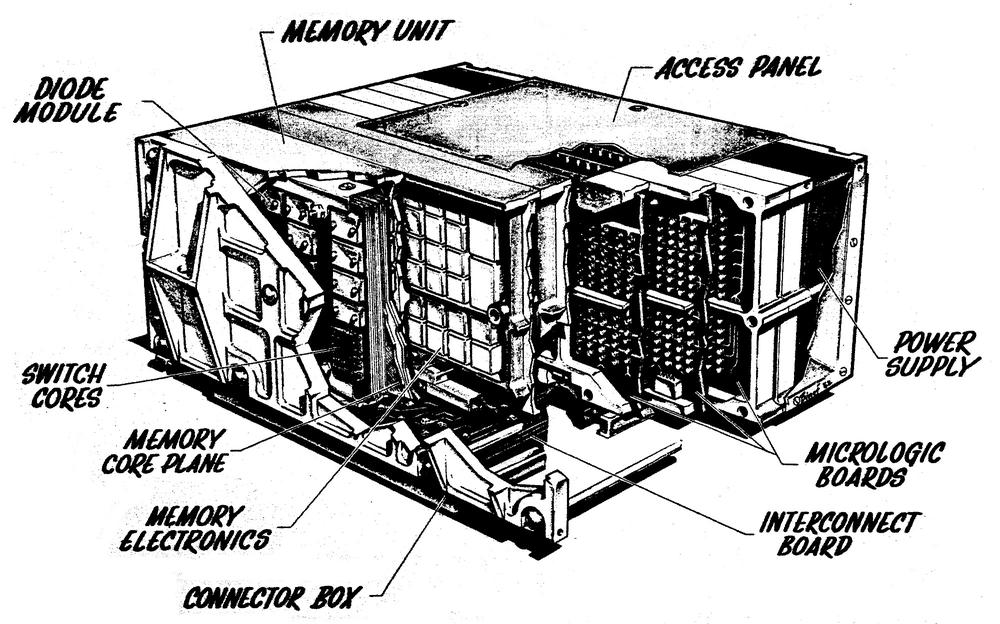

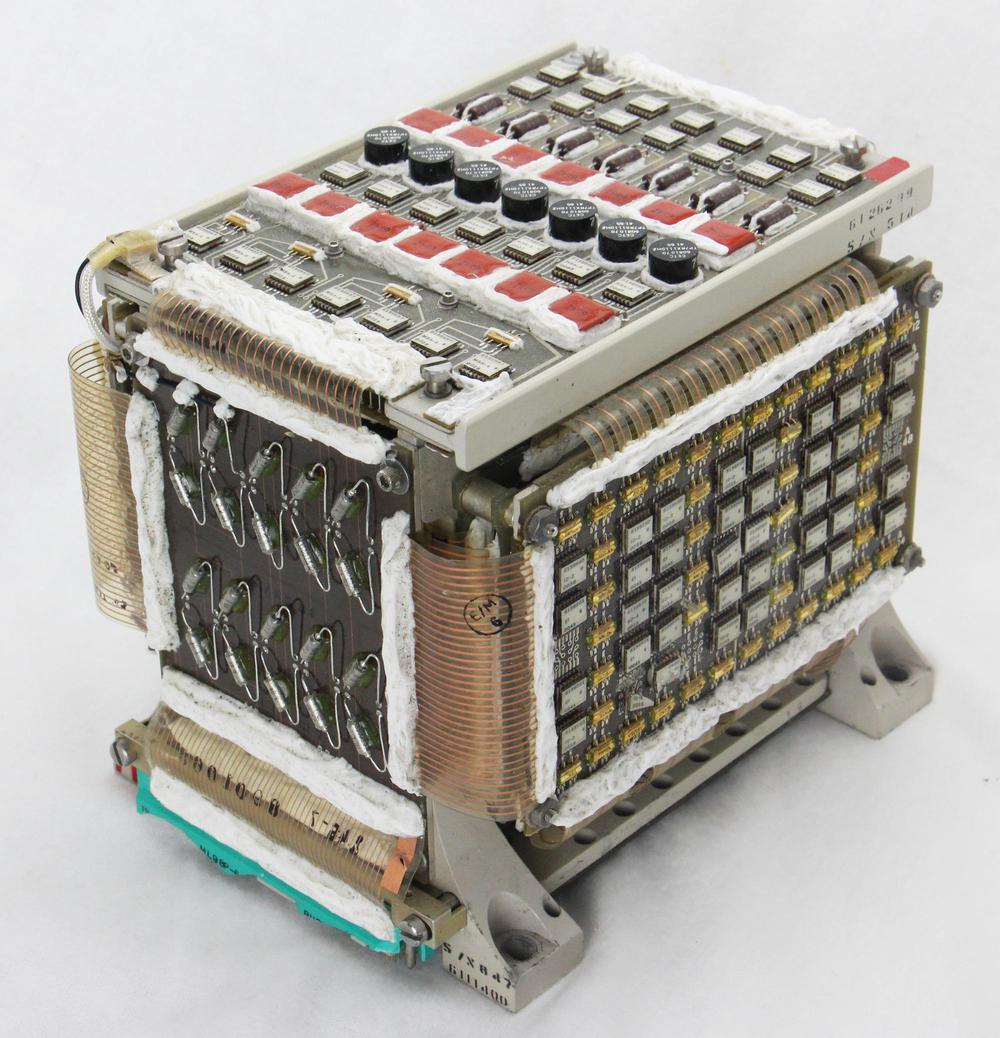

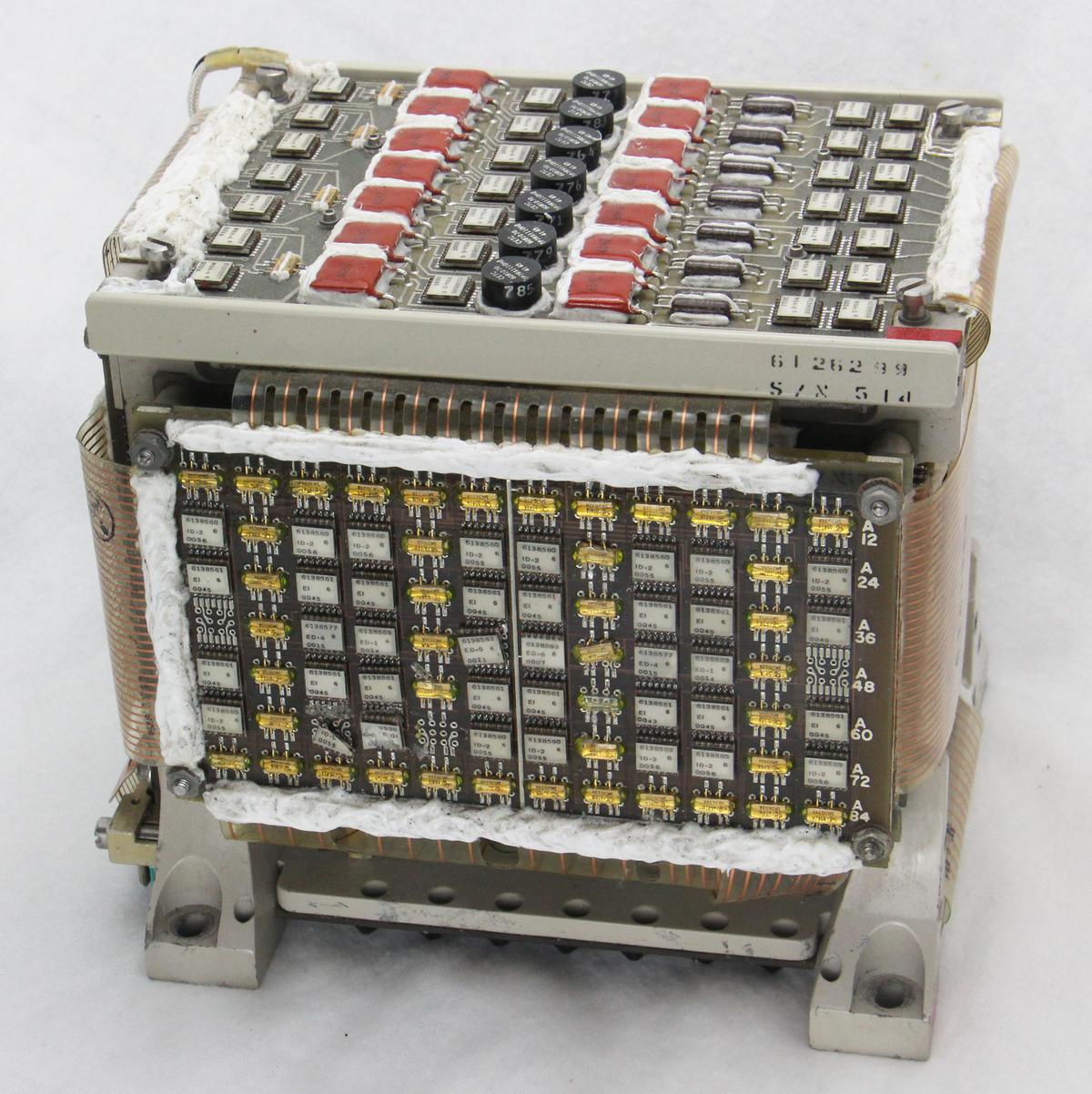

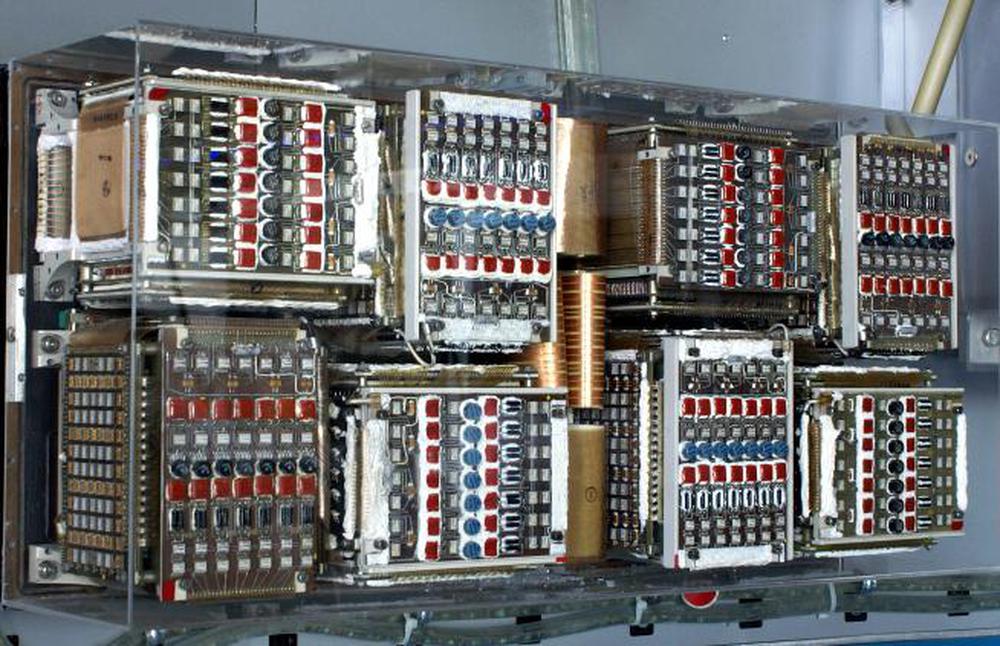

This computer, called the Magic 352, is a 20"×16"×9" black box2 weighing 80 pounds, surprisingly heavy for something used in a rocket.4 Its sturdy aluminum case alone weighs 20 pounds. Internally, the computer is divided into thirds. The front section holds the processor and the core memory storage. There is no microprocessor in this computer; the processor is built from hundreds of simple integrated circuits. The back section of the computer holds the interface boards, mostly analog circuitry to connect to the rest of the rocket.5 Unexpectedly, the middle section is mostly empty space.6 The computer was made by Delco, a division of General Motors3 that built a whole line of "Magic" aerospace computers.

The digital side

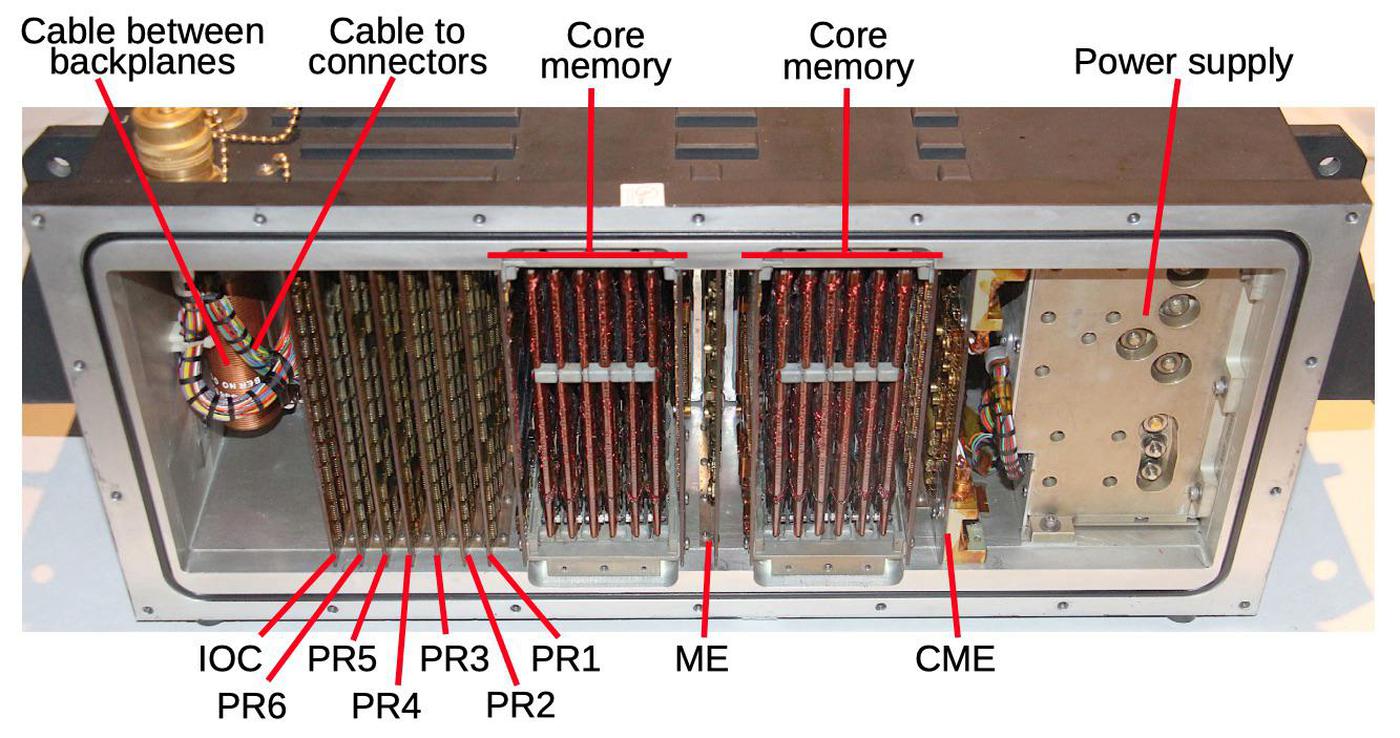

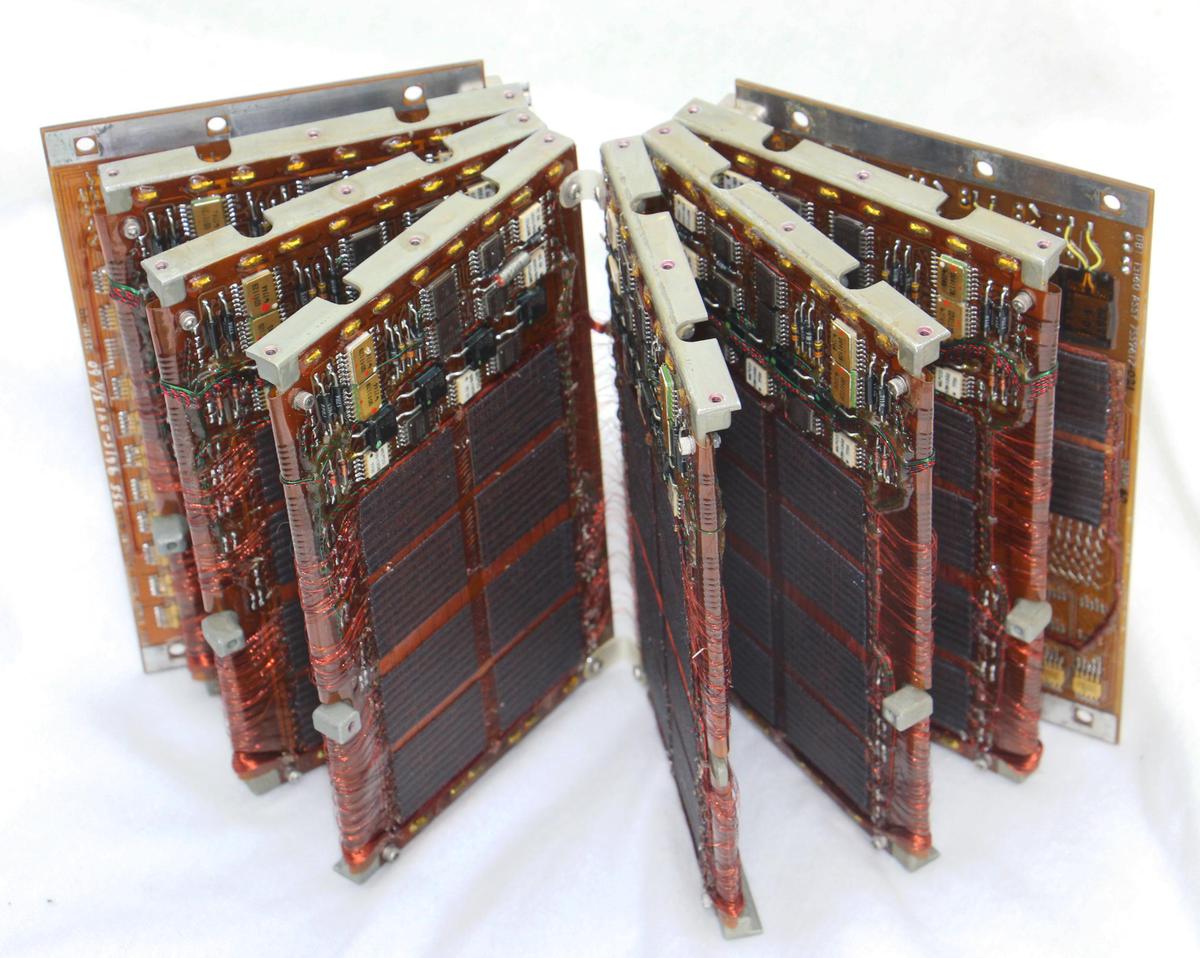

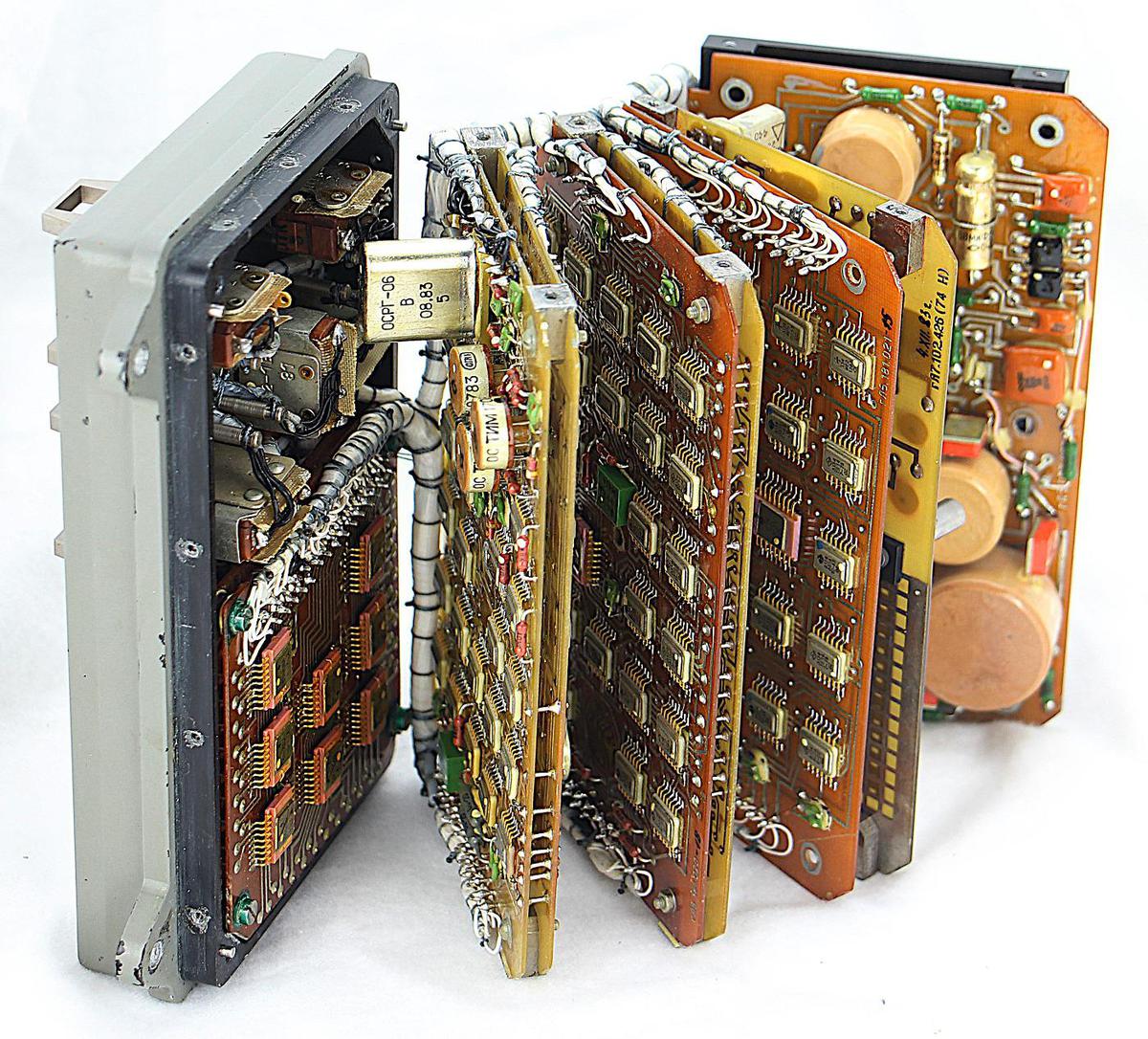

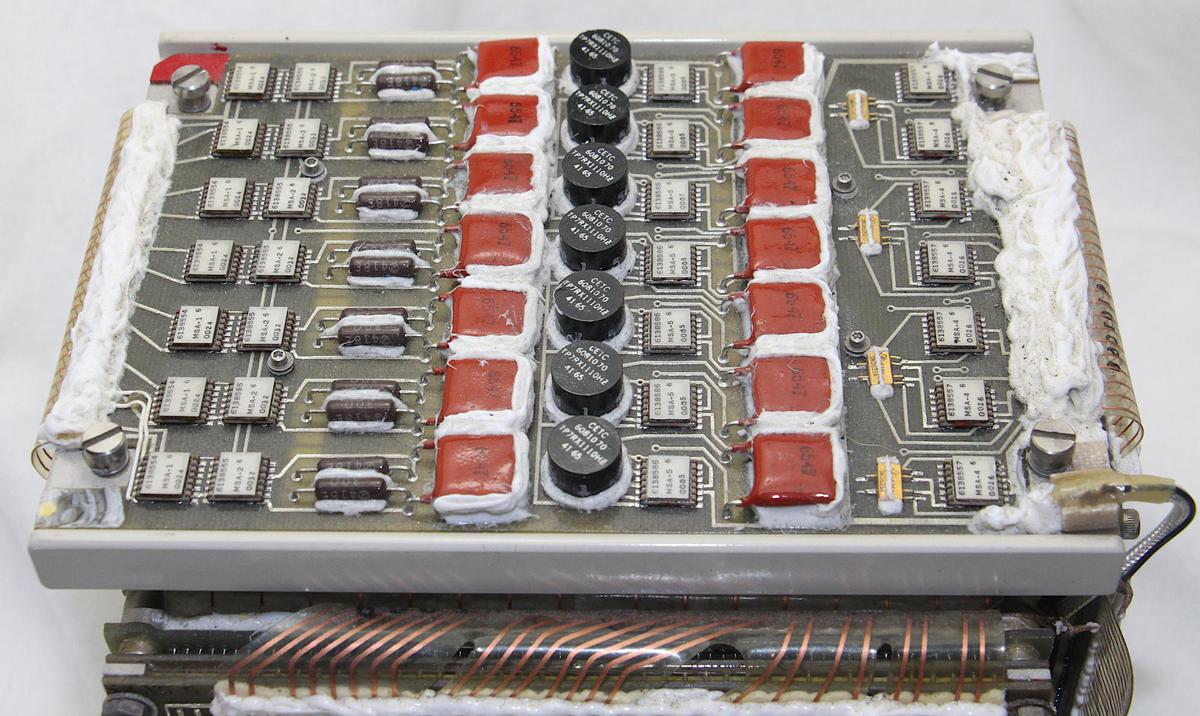

The computer's front cover is held on by 18 screws. Removing them reveals the computer's processor boards and core memory. On the left are seven circuit boards with TTL digital logic. In the middle are two core memory modules, each holding 8192 words of 24 bits. Two memory electronics boards are next to the memory. At the right is the computer's switching power supply.

The circuit boards have alphanumeric codes on them; PR1 through PR6 are probably processor boards 1 through 6. It's unclear what "IOC" stands for; the IOC board looks like the other digital logic boards, but also has a circuit that's probably the computer's clock. The "ME" and "CME" boards appear to have high-current driver circuitry for the core memory modules, so "ME" could be "memory electronics".

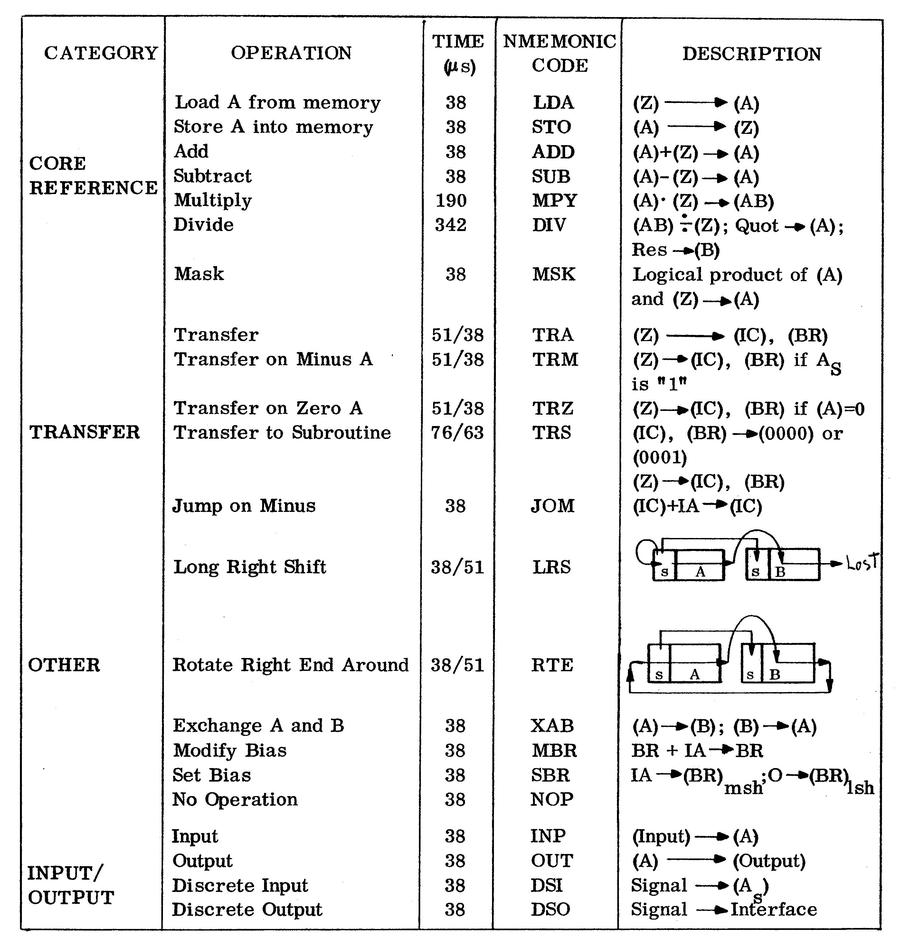

Information on the Magic 352 computer is hard to obtain7 but it uses 24-bit words (plus a parity bit), and it uses 2's complement fixed point. It has 57 instructions (probably two per word) and can do an add/subtract in 6 microseconds. The processor has six index registers.

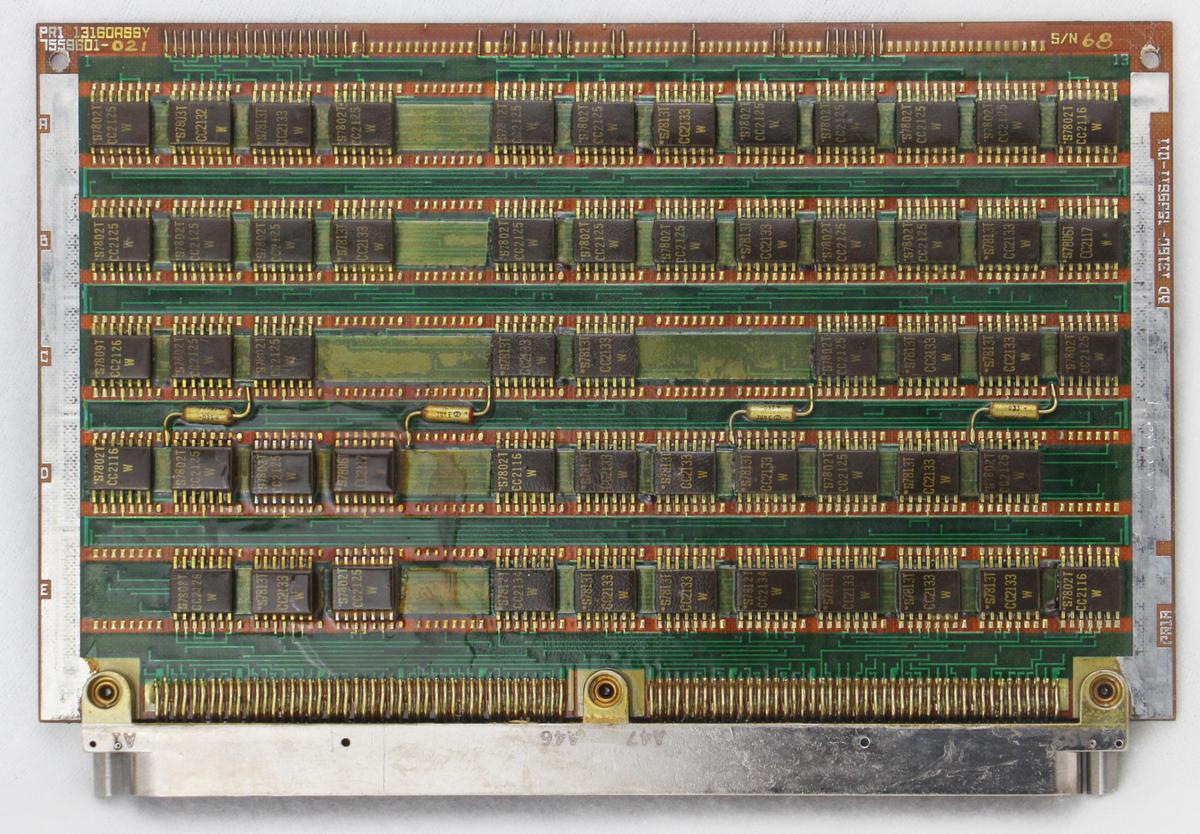

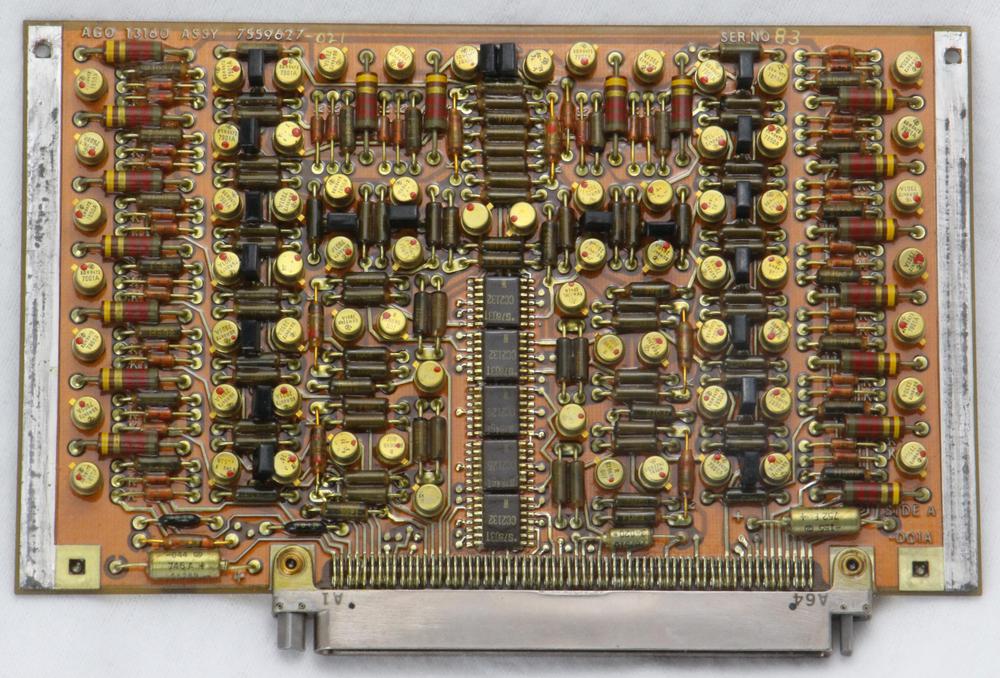

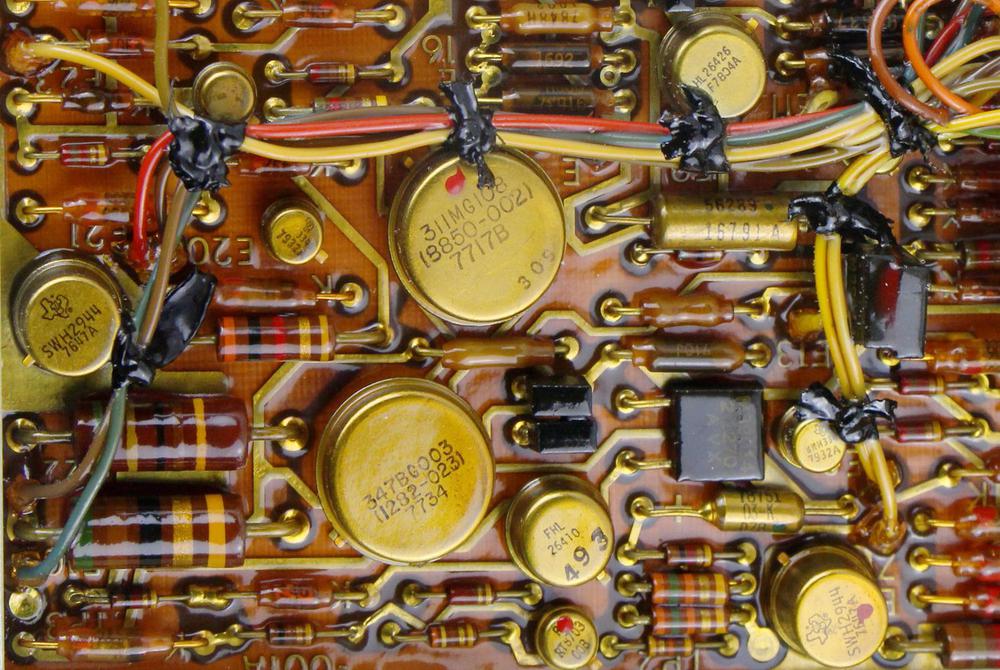

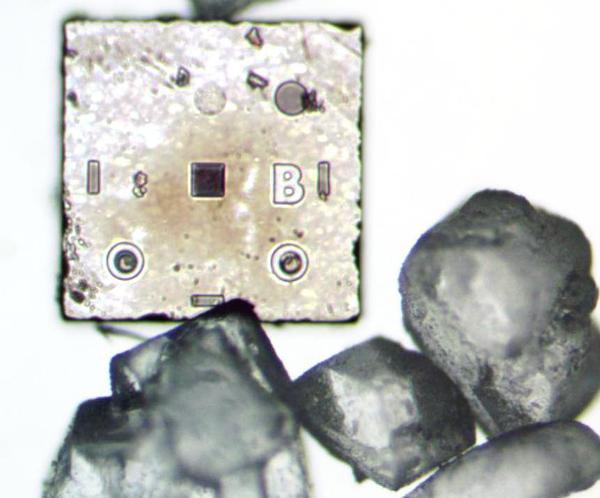

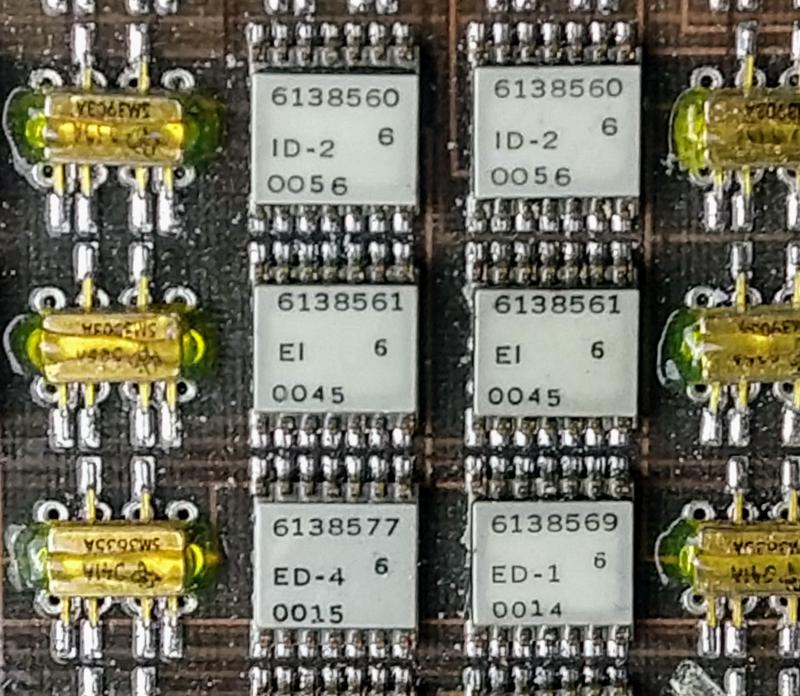

The photo below shows one of the digital logic boards; the other digital boards are similar. Each board has integrated circuits on both sides, so the back looks about the same. (My photo album of all the boards is here.) Each side of the board has space for 5 rows of 13 chips, for up to 130 chips per board. The printed circuit board appears to have six layers; two wiring layers and a ground plane for the chips on each side. Connections between the two sides are done through the 99 connections at the top of the board rather than vias. The boards are covered with conformal coating to protect the circuitry; decades later, the coating still smells strongly of turpentine. The edges of the boards are metalized and slide tightly into card guides, providing a path for heat to escape since there is no fan. The digital boards have a 198-pin connector at the bottom that plugs into the backplane, while the interface boards (discussed later) have a smaller 128-pin connector.

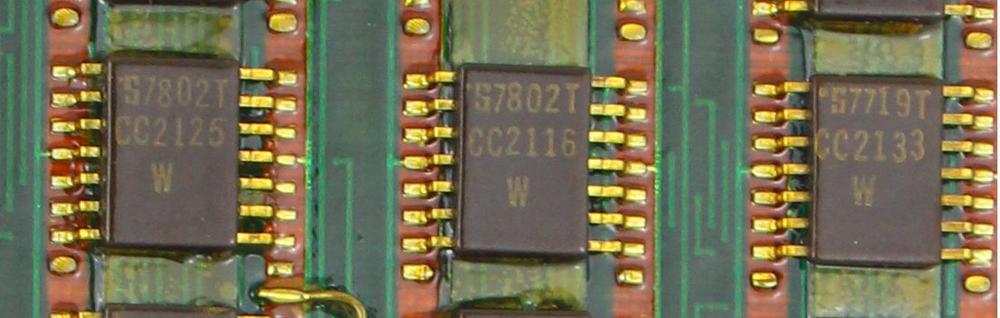

The boards are filled with TTL chips, probably MSI (medium-scale integration) chips such as counters, adders, or shift registers. Note that this computer does not contain a microprocessor chip, but has a processor built from simple building blocks. (In the 1970s, minicomputers were commonly built from boards of TTL chips.) From the part numbers on the chips, they appear to be manufactured by Signetics, in a CC2100 series. Unfortunately, even after extensive searching I couldn't find any documentation on these part numbers. (Please let me know if you have information on them.)

One interesting feature of the boards is they are keyed to ensure that a board can't be plugged into the wrong slot. The keying is implemented by splitting a hex nut in half. The circuit board and the backplane connector have matching halves, so the board can only be inserted into the right slot. There are six ways to split a hex nut corner-to-corner, and two hex nuts (one on the top and one on the bottom), making 36 possible keying combinations. The photo below shows part of the backplane with the boards removed so the connectors and half hex nuts are visible. Note that each connector has hex nuts at a different angle for the keying.

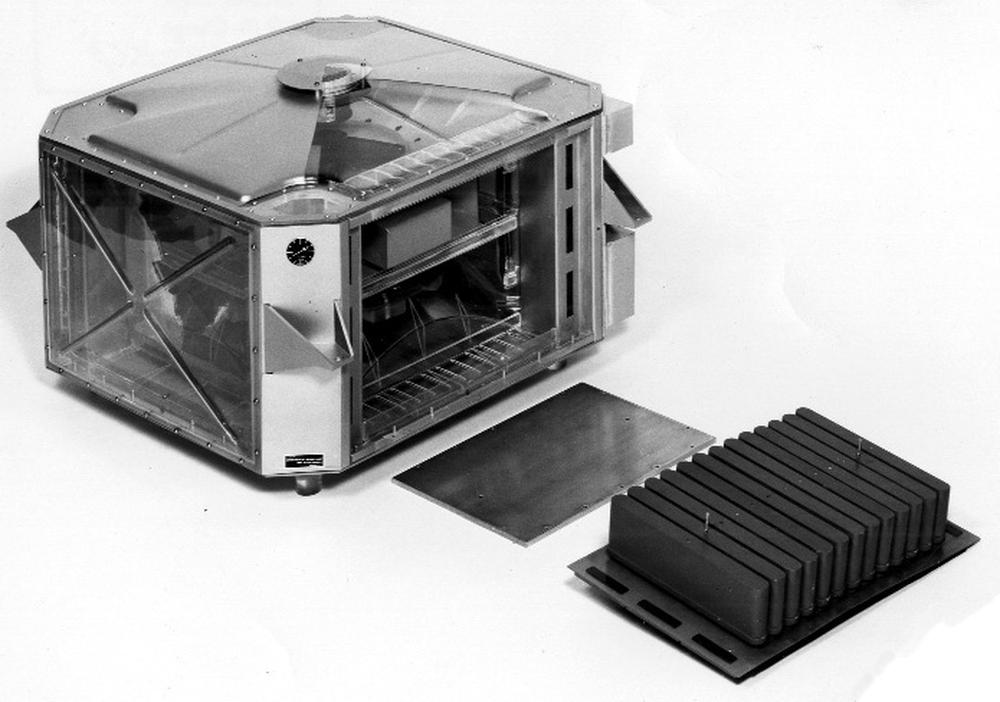

Core memory8

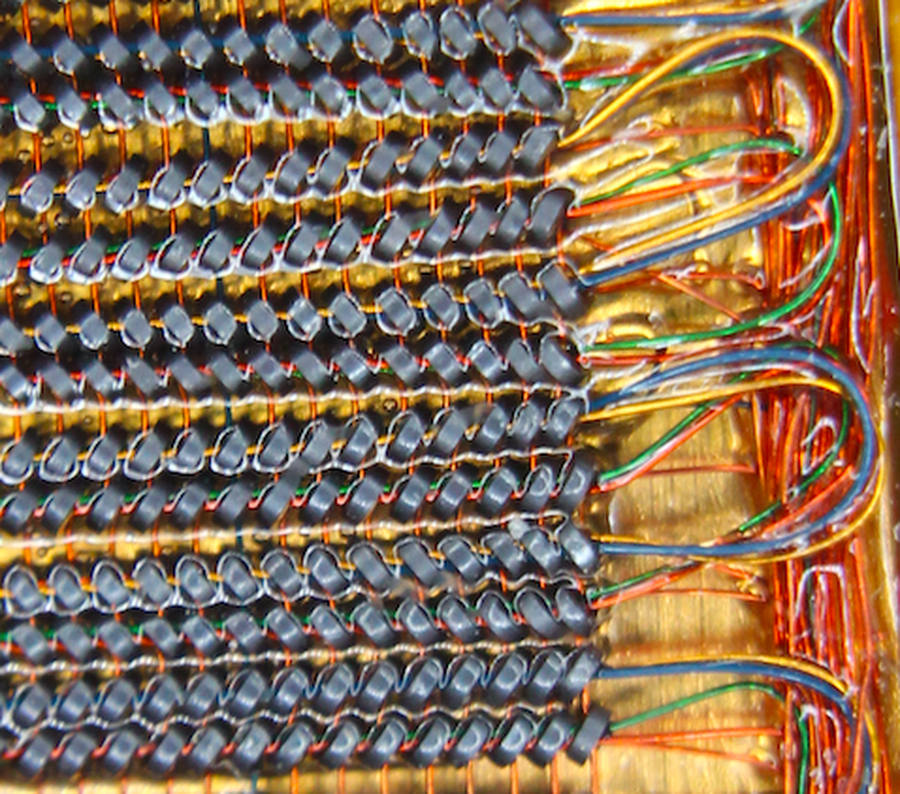

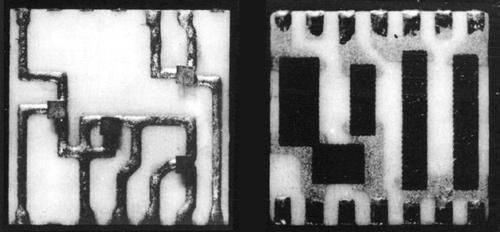

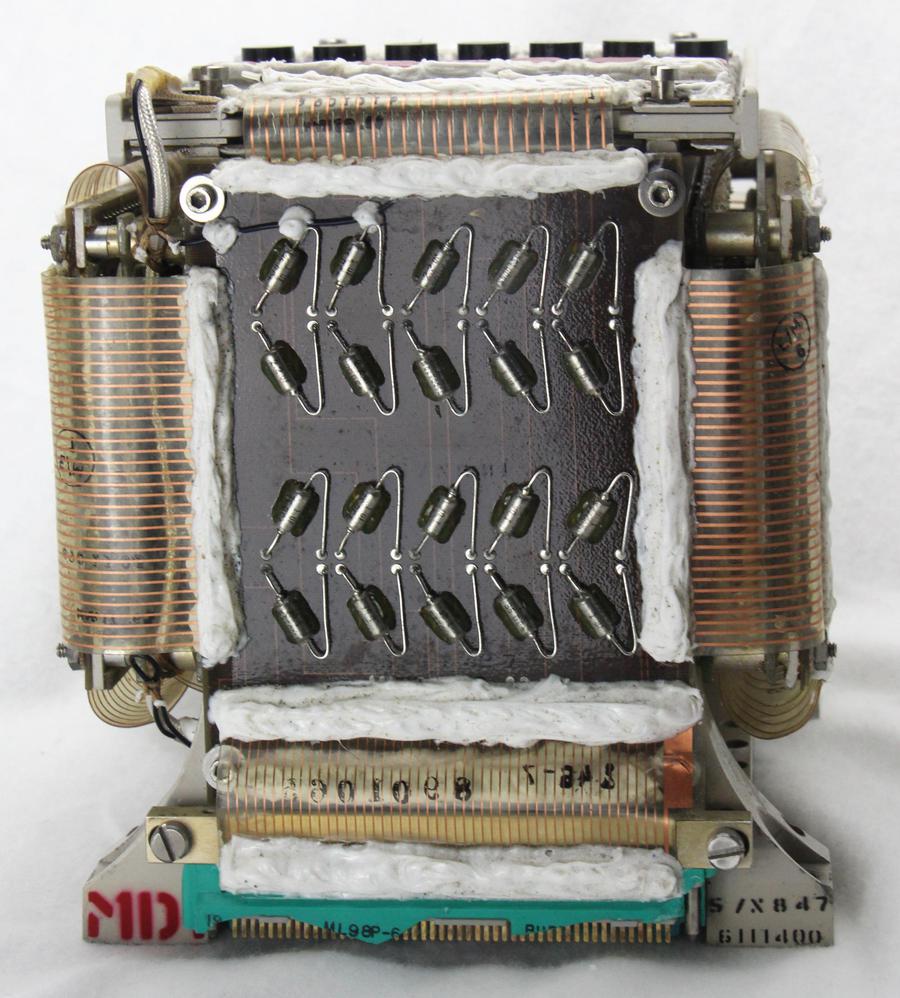

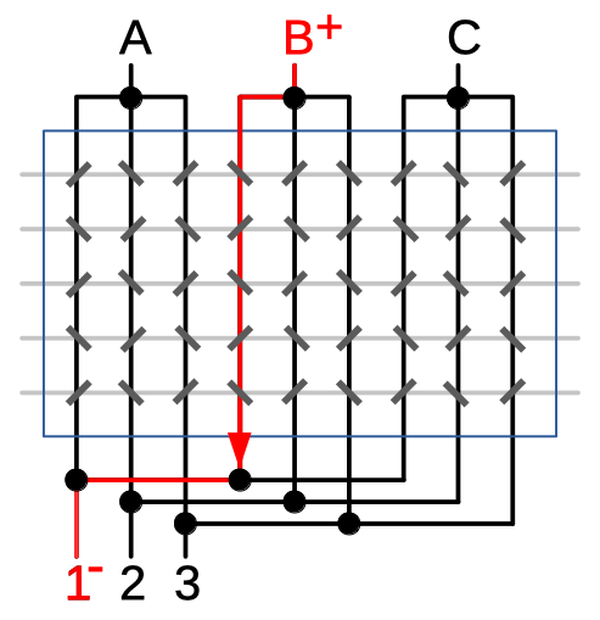

This computer uses magnetic core memory for storage (in contrast to the earlier Titan ASC-15 computer, which used a rotating magnetic drum). Core memory was the dominant form of computer storage from the 1950s until it was replaced by semiconductor memory chips in the 1970s. Core memory was built from thousands of tiny ferrite rings called cores, with one bit stored in each core. A core was magnetized either clockwise or counterclockwise to store a value. Cores were arranged in a grid called a core plane; energizing a specific row wire and column wire selected the particular core where the two wires crossed.

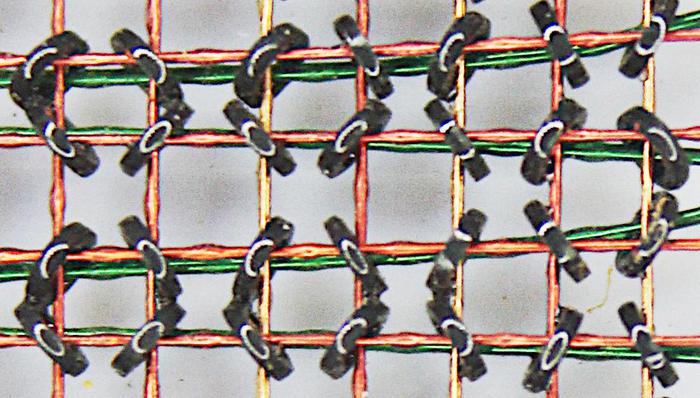

The photo below shows a closeup of the tiny magnetic cores in the Titan computer. There are four wires through each core: the vertical and horizontal red wires form the grid to select a core. Two colorful horizontal wires pass through each core in the plane: the sense line (used for reading) and the inhibit line (used for writing). You can see these wires looping from row to row at the right.

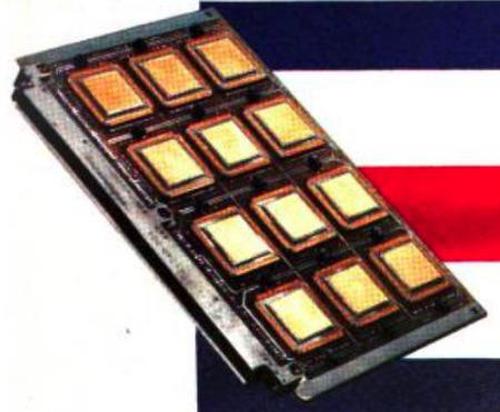

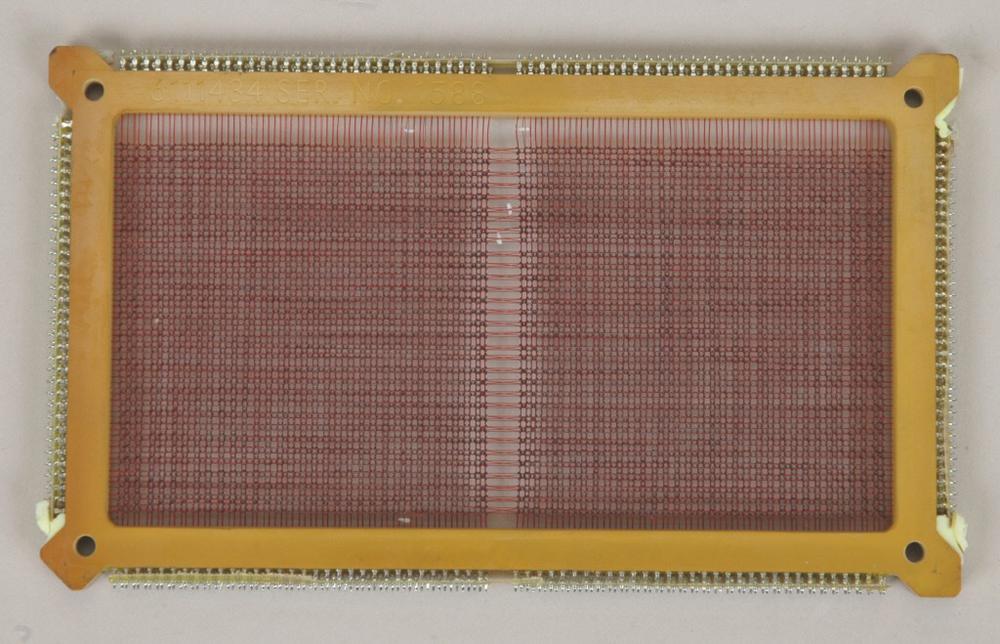

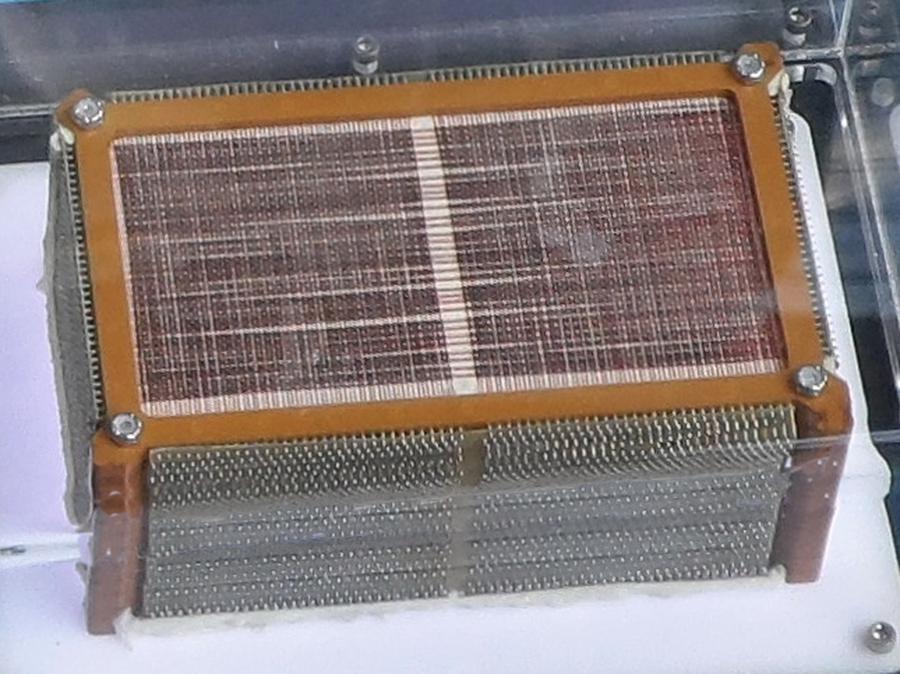

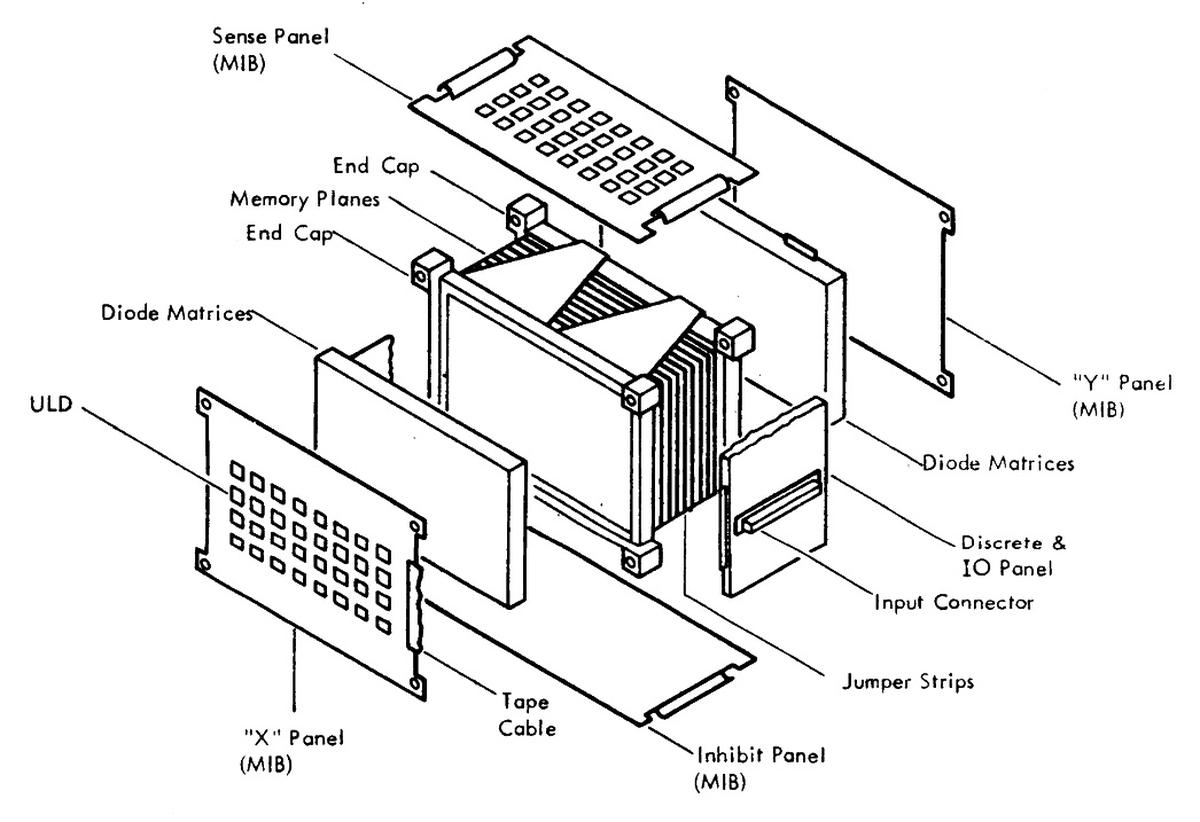

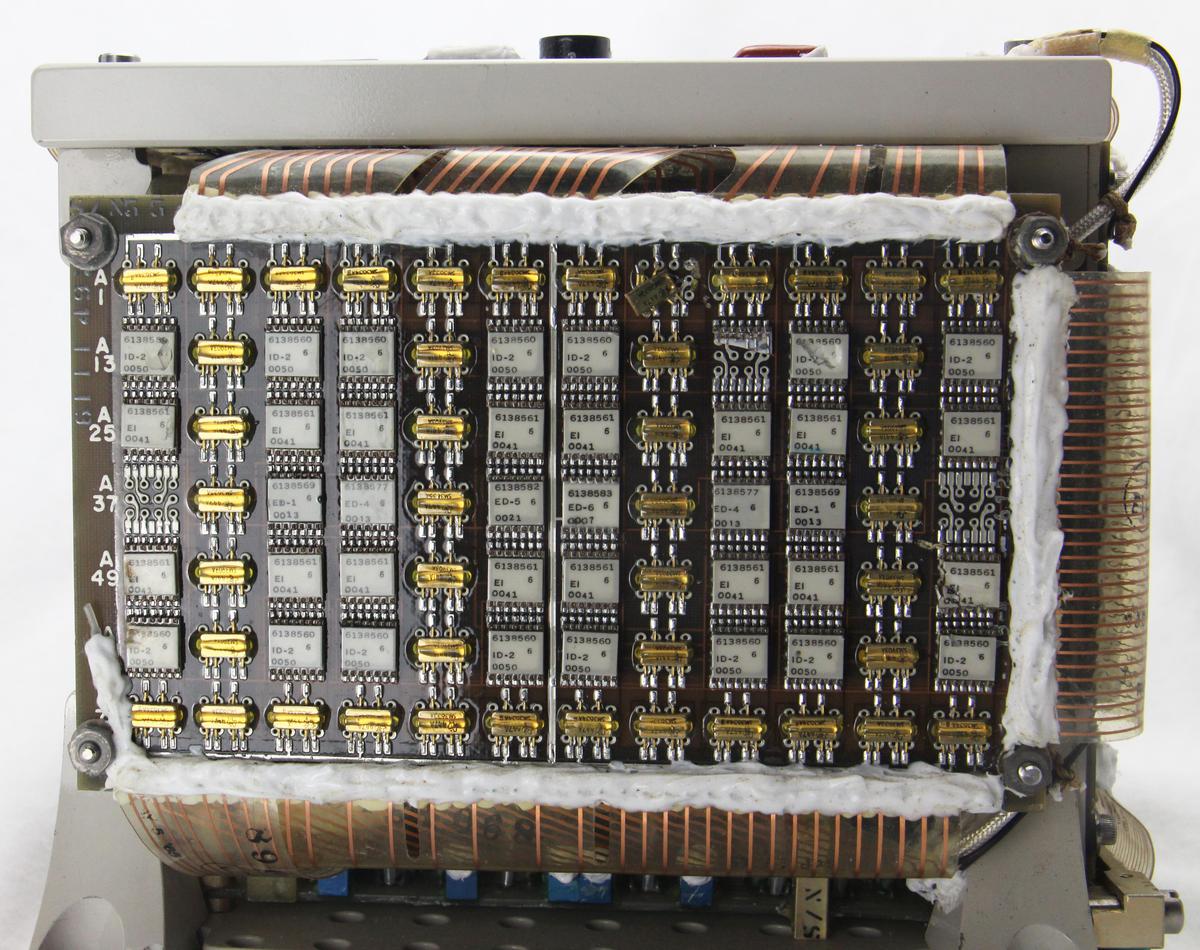

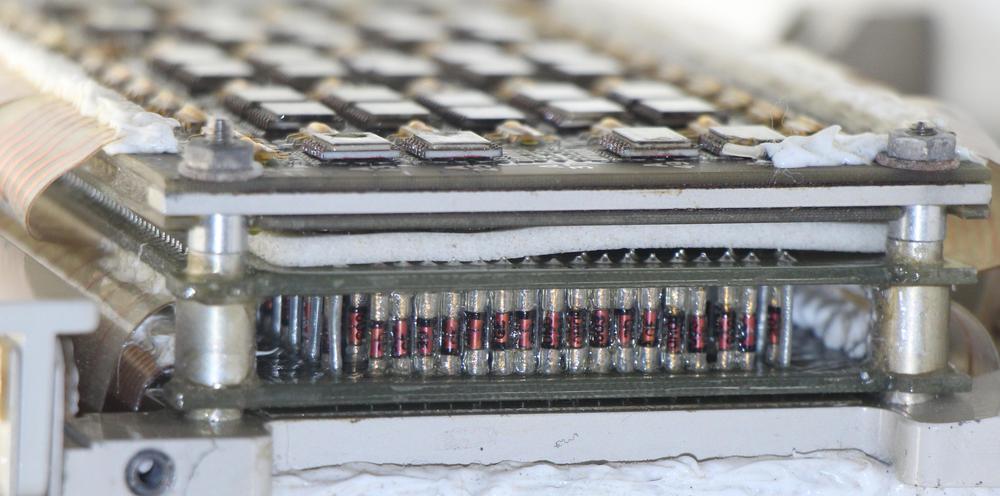

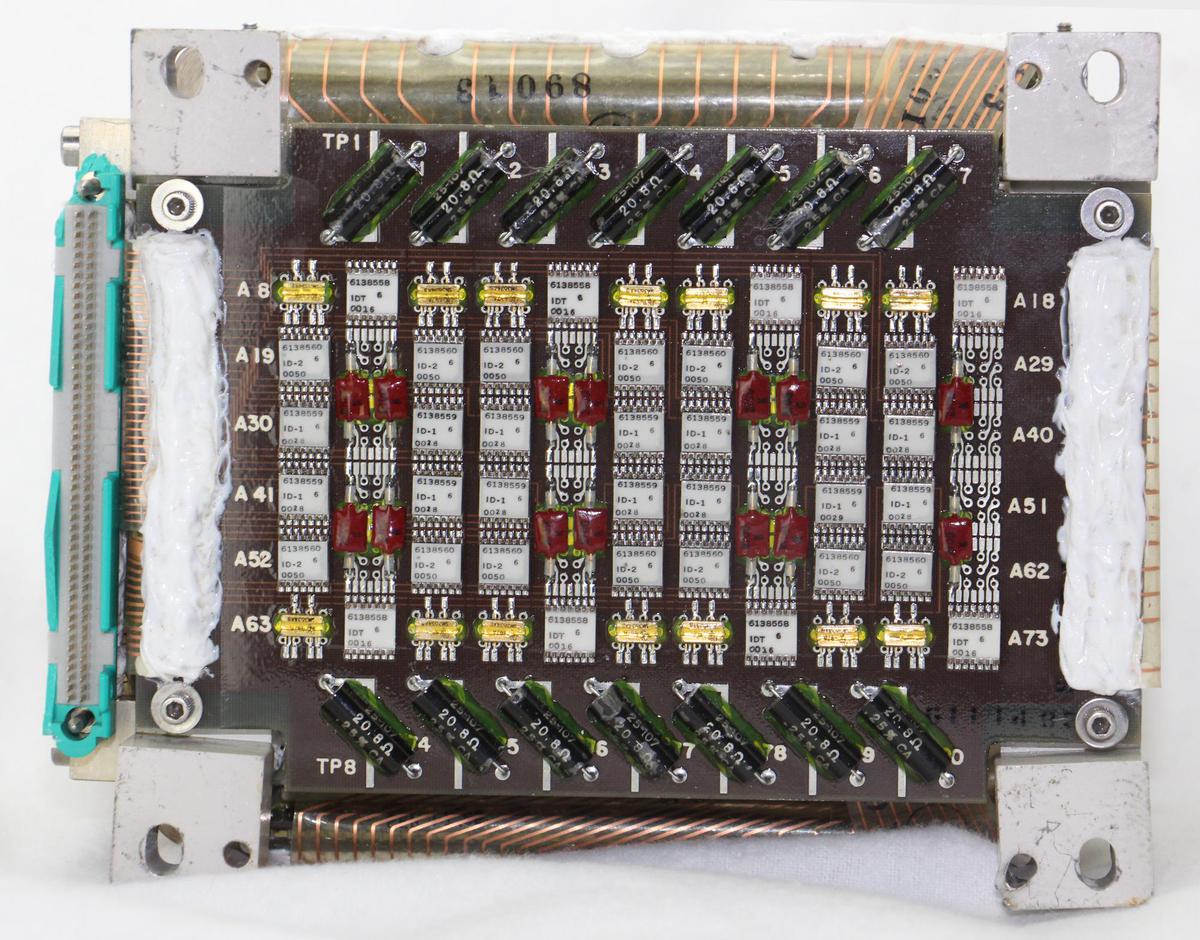

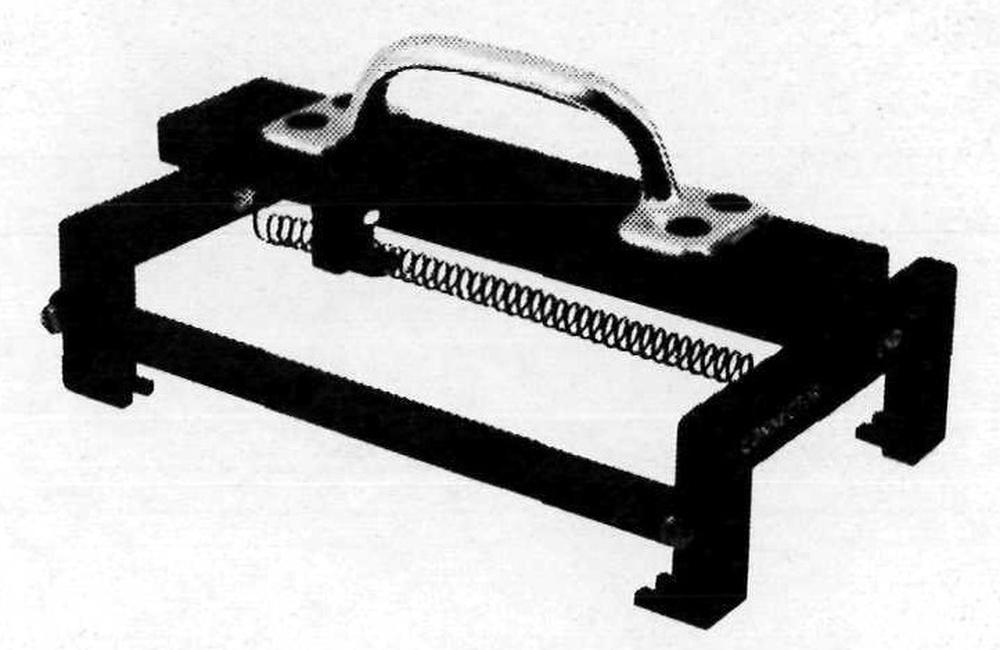

In a core memory, multiple planes are stacked together, one plane for each bit in a word. In most computers, the core planes were welded or soldered together into a block, but the Titan computer's core memory was built with an unusual patented technique: the cores and the circuitry were mounted on a long flexible printed circuit board that was folded accordion-style. This construction technique allows a core memory module to be opened like a book to access the cores and circuitry.

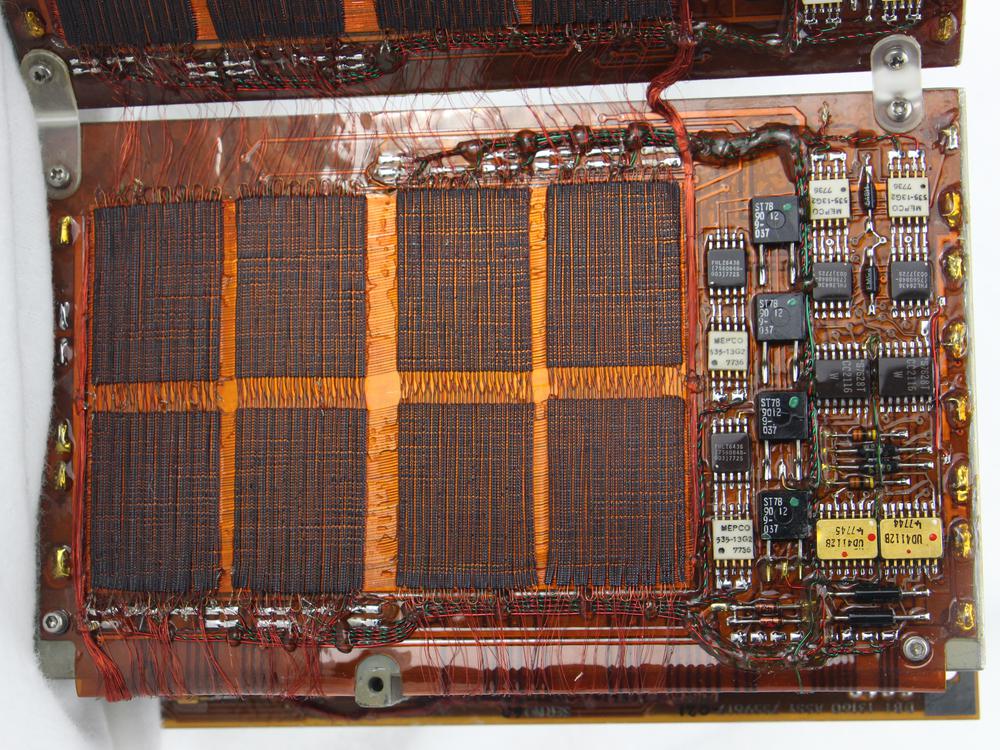

If you view the core memory module as a book, each "page" is constructed from a metal plate with the flexible printed circuit board wrapped over both sides. There are 6 of these "pages", so there are 12 core memory planes similar to the one below. Careful counting shows there are 128 horizontal wires and 128 vertical wires through the core plane, so there are 16,384 cores below. The 128 vertical wires are visible at the top and bottom, running loosely from plane to plane. Note that these are the delicate wires through the cores, passing continuously and unprotected through the entire set of core planes. The 128 horizontal core wires are gathered into bundles to run from plane to plane; the left bundle proceeds downward, and the right bundle proceeds upward.

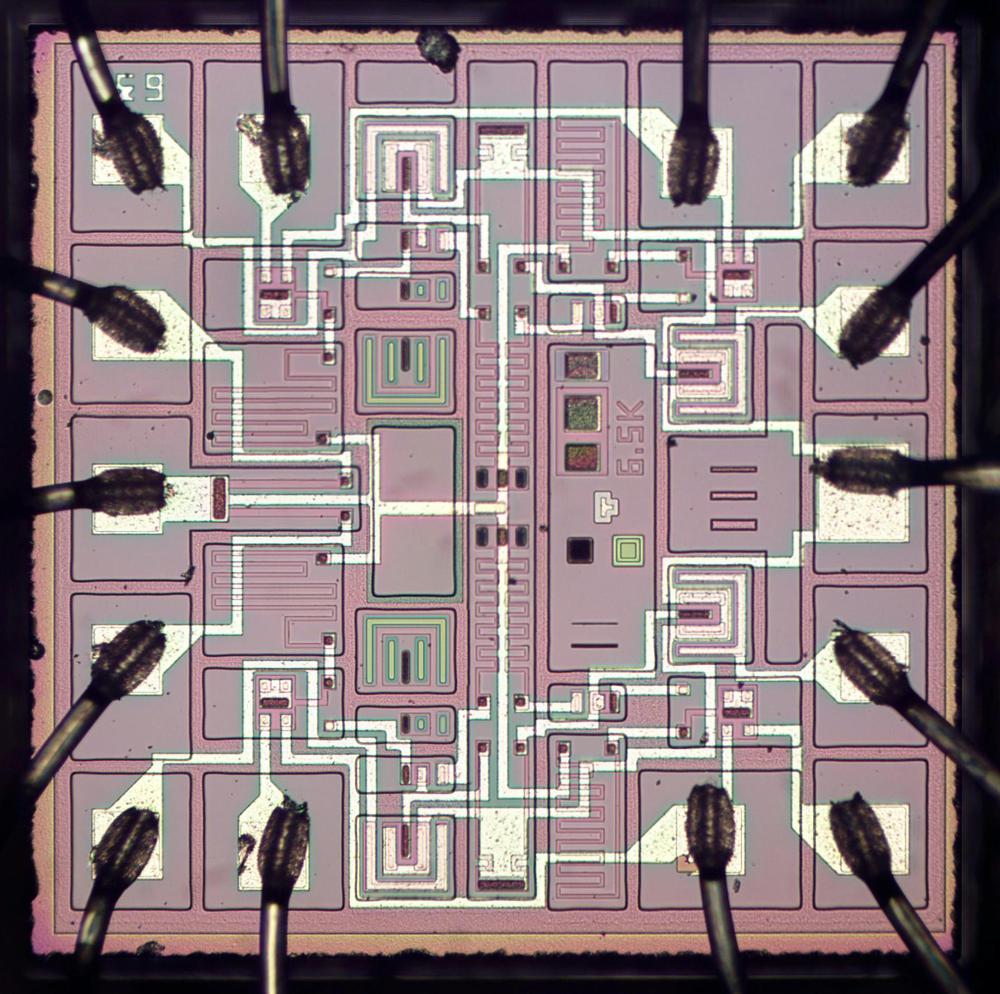

To the right of the cores (above) is the circuitry to handle that plane. This circuitry includes sense amplifiers to read the signals from the core plane, and inhibit drivers for writing data to the plane. These integrated circuits are mounted on the same flexible PCB as the core planes.

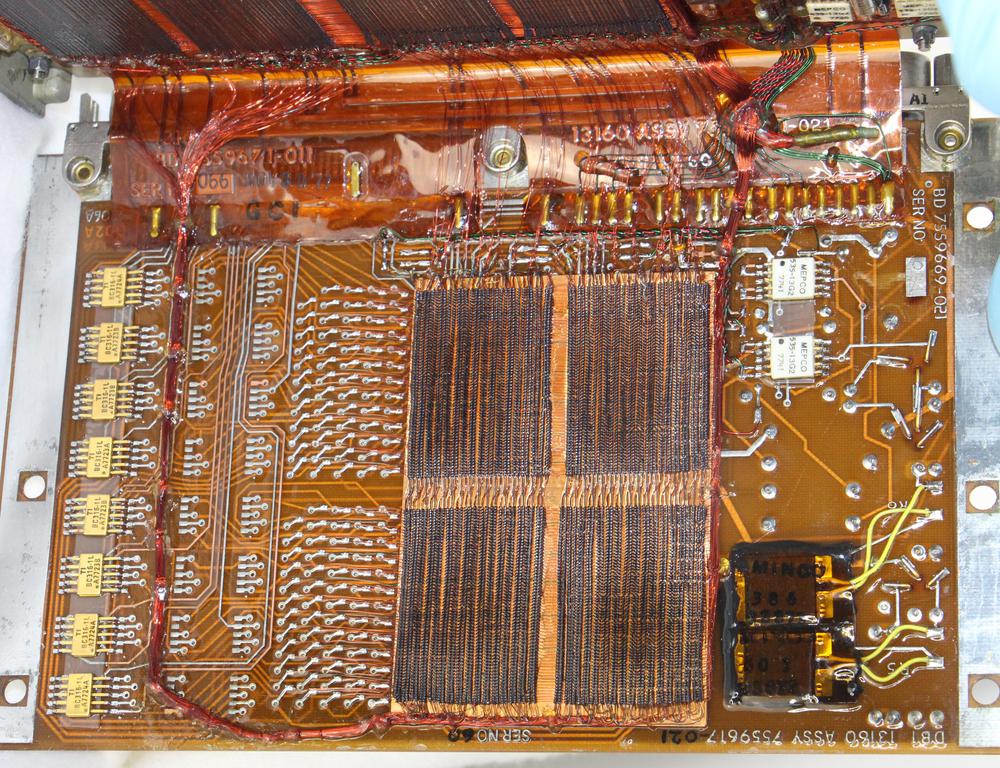

The flexible printed circuit board is attached to standard rigid printed circuit boards at both ends; these boards form the outside of the module. The end boards also have connectors that plug into the backplane, providing the connection between the core modules and the computer. The photo below shows one of the end boards. Note that this board has just half the cores of a normal board.9 The reason is that this board holds the parity bit, while the other 12 planes each hold two bits. Thus, the complete module holds words of 24 bits plus one parity bit, with 8192 words in the module. The computer has two core modules, so it holds a total of 16K words.10

The interface circuitry

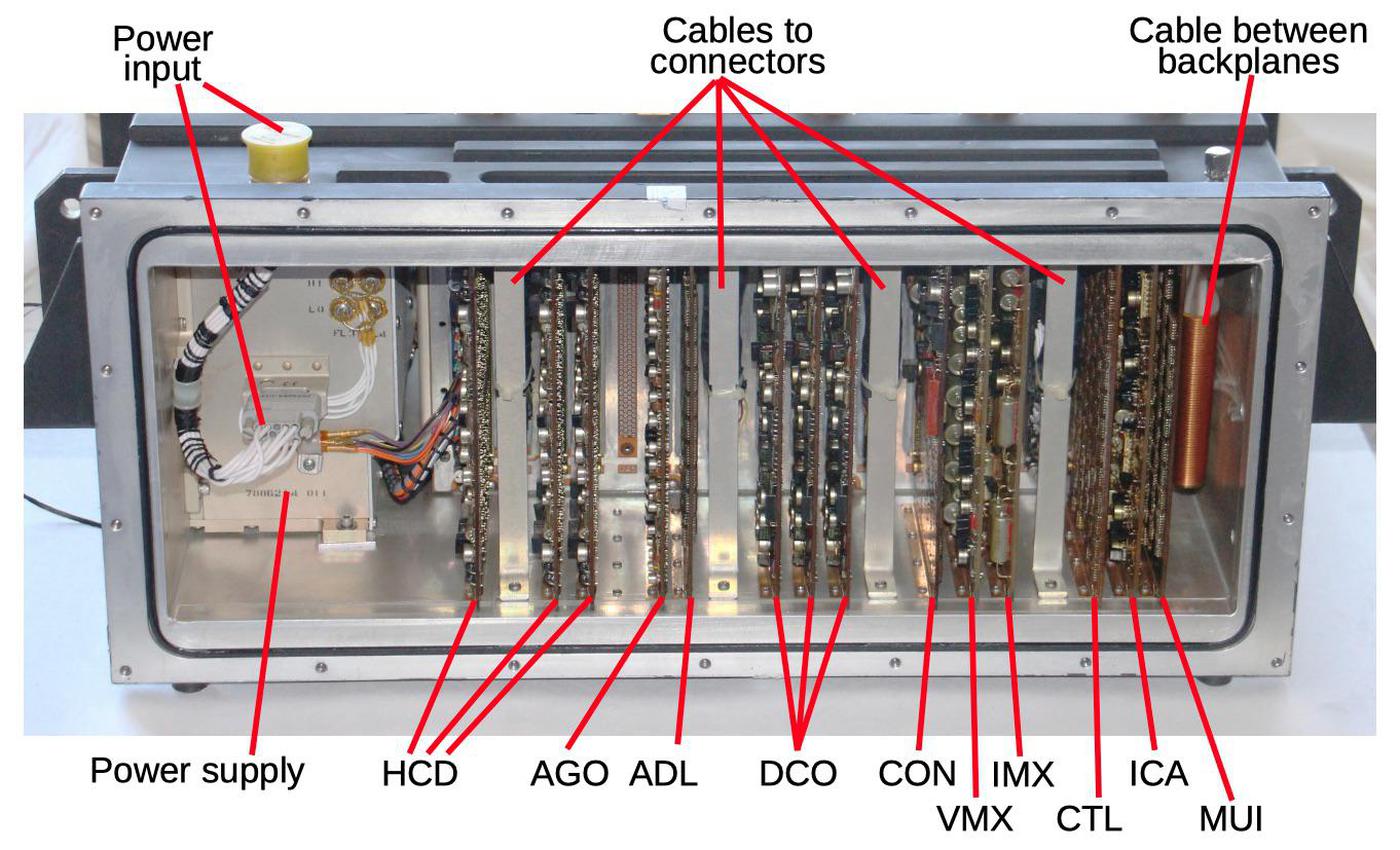

Turning the computer around reveals the circuit boards behind the back panel. These interface boards are wired to the connectors on top of the computer. Through these interfaces, the computer receives velocity and attitude pulses from the inertial measurement unit (IMU). The computer sends analog control signals to various actuators, as well as discrete (binary) signals to other parts of the rocket for thrusters, staging, and other functions. On the left is the power supply. The power supply receives power from the rocket through the connector on top of the computer and the cable to the power supply.

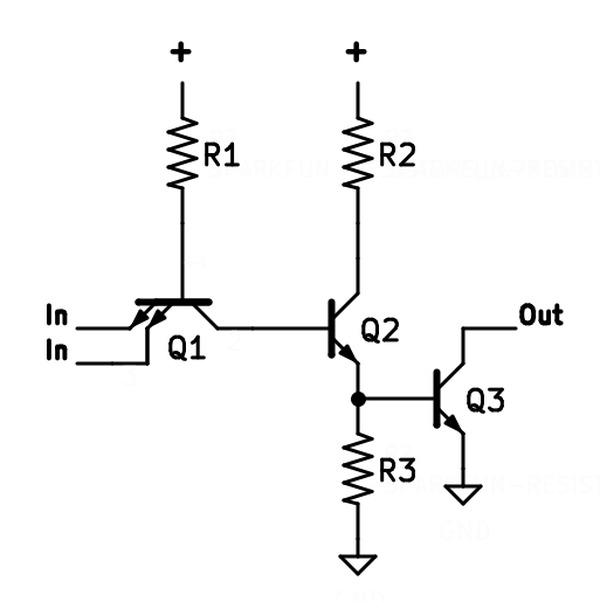

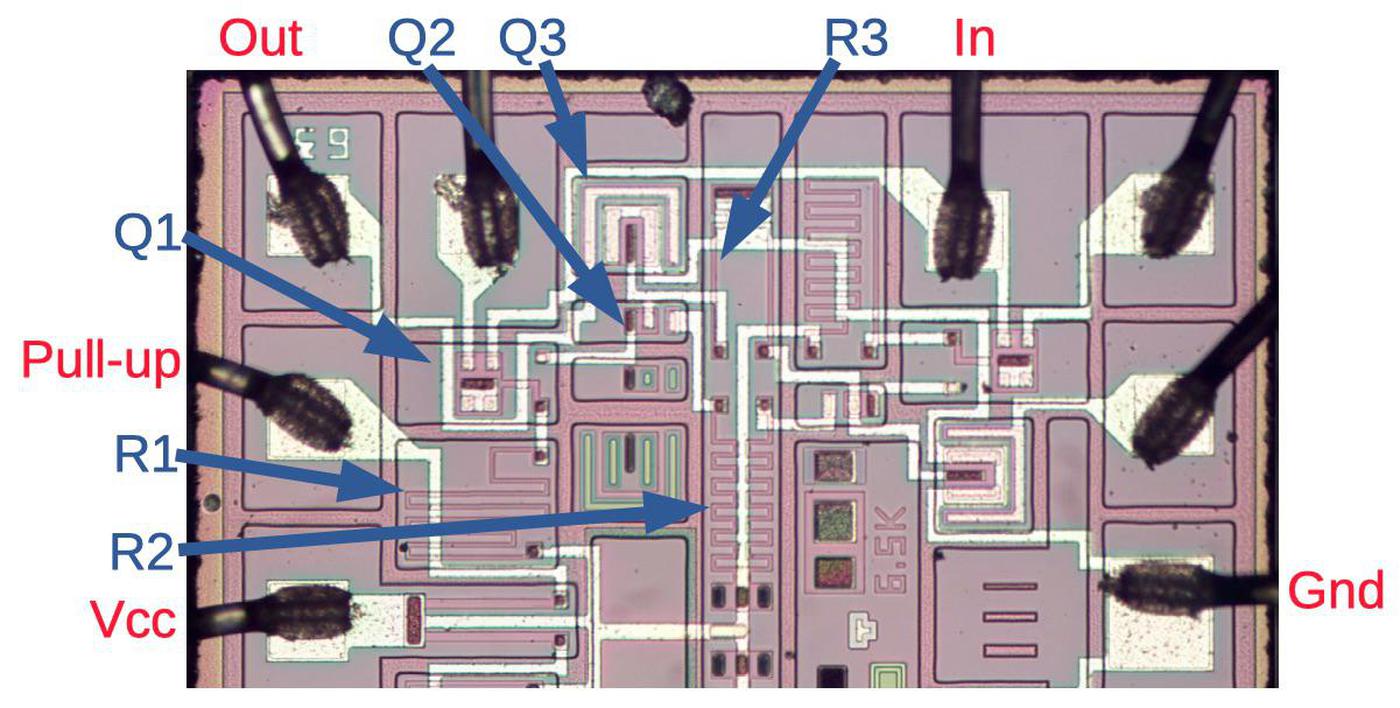

In contrast to the digital boards, which all appear similar, the interface boards have a wide variety of circuits. The CTL, MUI, and ADL boards are covered in TTL chips, similar to the boards in the digital section. The rest of the interface boards, however, are crammed with analog components such as transistors, capacitors, resistors, diodes, and hybrid modules, along with a few TTL chips. The interface boards have the analog components on the front only (probably because there isn't enough clearance on the back) and usually a few TTL integrated circuits on the back. I traced out some of the circuitry on the "AGO" board below and found 18 current-controlled outputs connected to TTL interface chips in the middle of the board. This board probably provides binary "discrete" outputs.

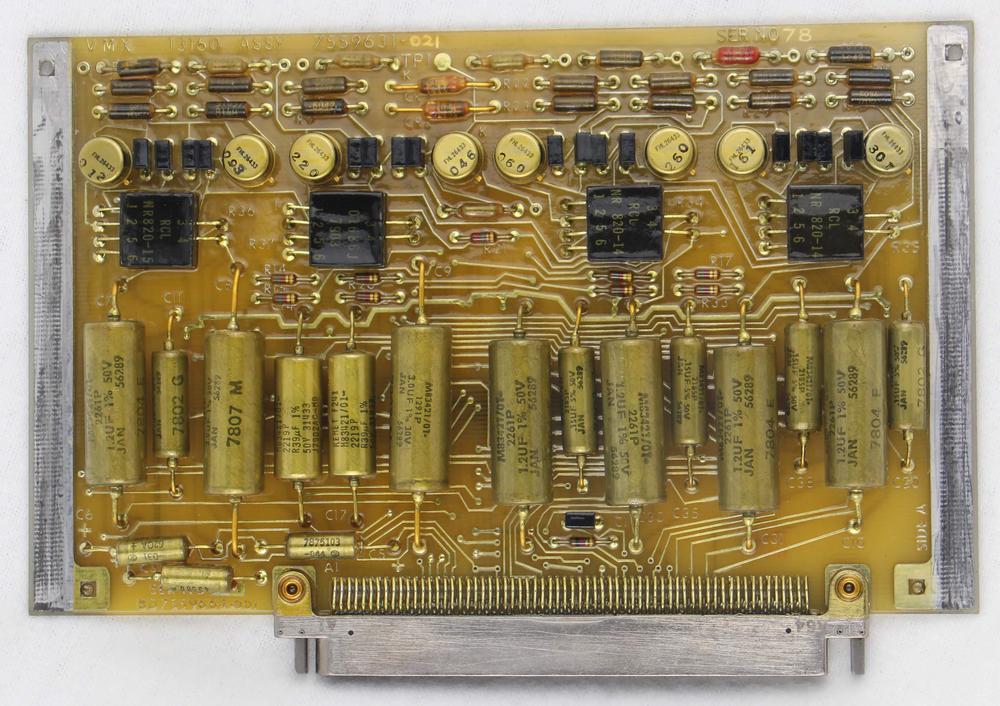

The VMX board below has four mysterious 6-pin black hybrid modules along with numerous large capacitors. It's unclear what function this board has, or why it needs so many capacitors.

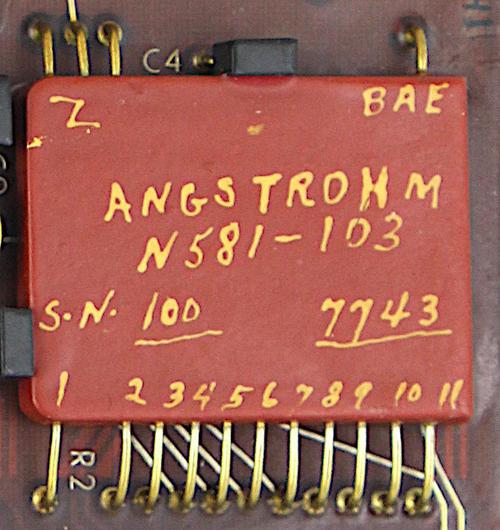

The CON board uses hybrid modules including a large red "Angstrohm" module that has hand-lettered labeling on it.

Power supply

The computer uses a switching power supply to efficiently convert the missile's power (probably 28 volts) to the voltages required by the computer. The power supply is surprisingly heavy, about 15 pounds. Much of the weight is probably metal needed to dissipate heat since there is no fan.

Inside, the power supply is packed with inductors and transformers, power transistors, and circuit boards. A stack of filter capacitors in large metal cans is visible at the left in the photo below. The inductors and transformers don't look like the inductors in commercial power supplies, but are black blocks.

Several circuit boards control the power supply. They use metal-can integrated circuits, unlike the integrated circuits in commercial power supplies. The part numbers on these integrated circuits didn't turn up anything useful so they may be custom military parts. The boards are covered with a conformal coating to protect them against humidity and other threats. The conformal coating gives a shiny golden color to the integrated circuits.

The power supply probably generates 5 volts for the TTL chips, along with a higher voltage to drive the core memory, and multiple voltages for the interface circuits.

History and background

In this section, I summarize the complex history of the Titan missile and rocket, and its various guidance computers. The Titan missile, deployed from 1959 to 1987 was the largest ICBM deployed by the United States and delivered a 9 megaton nuclear bomb. To get a sense of how large the Titan was, the currently-deployed Minuteman missile weighs a third as much and its warhead has 1/25 the yield.

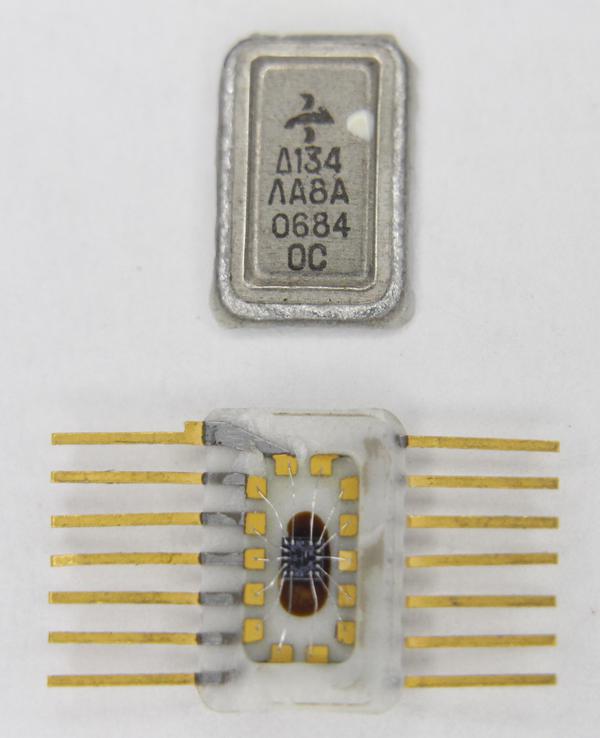

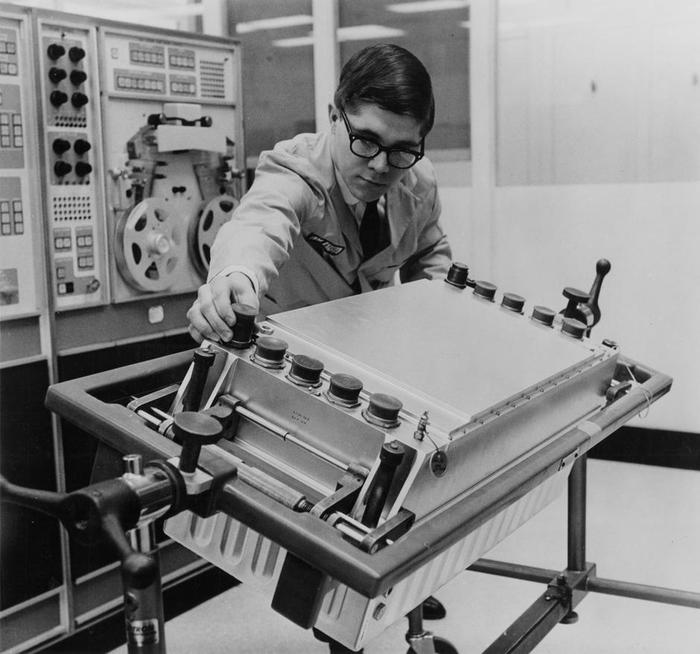

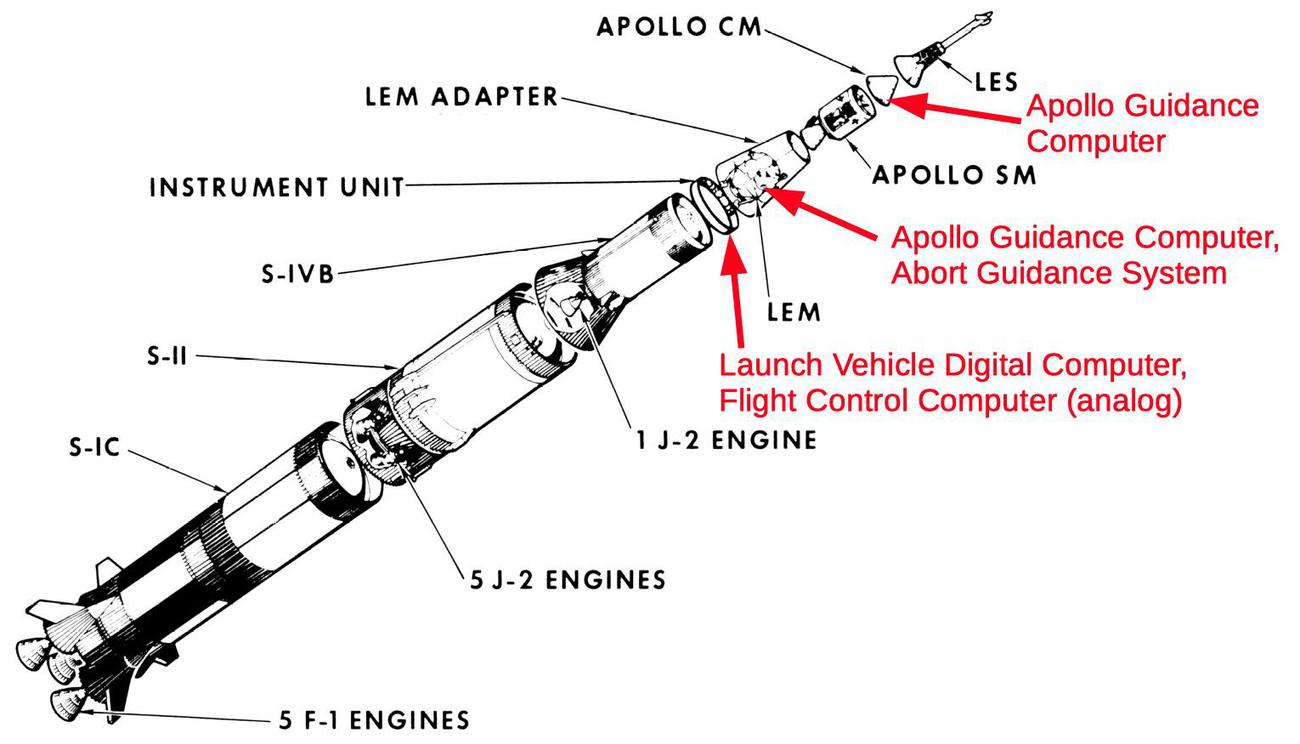

For much of its life, the Titan II's guidance computer was the IBM ASC-15 (Advance System Controller), dating to 1962. This was a 27-bit serial, transistor-based computer using discrete components in welded encapsulated modules. For storage, it used a rotating magnetic drum that held 3,840 words. This computer was used on the Titan II and Titan III, as well as the early Saturn I flights.11

Around 1964, the Titan II missile was modified for use as a satellite launcher called the Titan III. The most visible change was the addition of two solid rocket boosters for many Titan III launches. The first Titan III flights continued to use the ASC-15 guidance computer, but the project switched to the Univac 1824M Digital Flight Control System. This computer was more powerful and able to handle flight control as well as guidance and navigation. It first flew on Titan IIIC on Feb 9, 1969. However, the Univac 1824 project ended in 1969 due to cost and schedule over-runs.

Meanwhile, the AC Spark Plug division of General Motors developed the Magic family of computers for airborne guidance starting in 1962; I wrote a detailed article on the Magic computers. Delco used some of these computers in an inertial measurement unit (IMU) guidance system called the Delco Carousel.12 The Carousel IV was a popular navigation system, used on commercial planes including the 747, 707, and DC-8. The Carousel IV used the Magic 311 computer (1967) and then the Magic 351 computer (1970).

The Carousel IV navigation system (with the Magic 351 computer) was turned into a military navigation system called the Carousel V, using the Magic 352 missile guidance computer (MGC). (This is the computer I examined in this blog post.) For space use, this system became the Universal Space Guidance System (USGS). The Titan IIIC rocket switched from the Univac computer to the USGS, first flying with it on December 13, 1973 (details). After its use on the Titan III, the USGS system was retrofitted onto the Titan II missile, replacing the obsolete ASC-15 (details) in a project called RIVET HAWK (1975-1976).

To summarize, the Titan program used several different computers as techology advanced, ending up with the computer I examined in the 1970s.

Conclusion

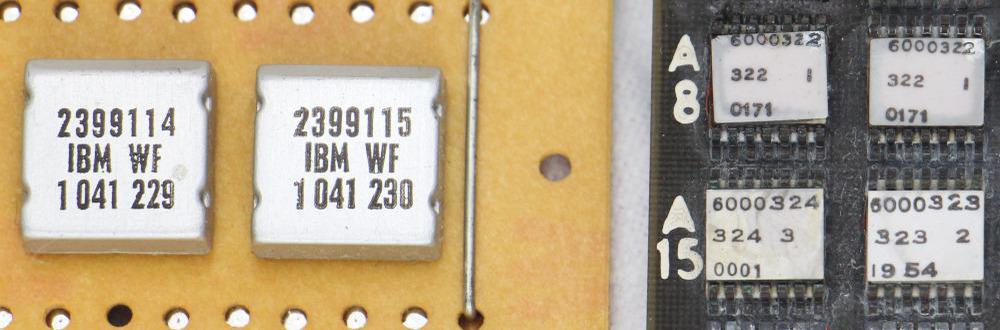

Aerospace computers are mostly ignored in computer histories, even though they used a lot of innovative technologies. This Titan missile, for instance, computer used flexible PCBs in its core memories. It also had surface-mounted integrated circuits, years before they were common in commercial electronics. Building computers out of TTL chips became a technological dead end, however, as the capabilities of CMOS integrated circuits increased exponentially, following Moore's law.

You can see photos of the full set of boards here; the interface boards are worth examining due to their varied circuitry. I announce my latest blog posts on Twitter, so follow me @kenshirriff for future articles. I also have an RSS feed. Thanks to Steve Jurvetson. for supplying the computer.

Notes and references

-

Guidance systems use a variety of algorithms, with earlier low-power computers using simple guidance algorithms, while later computers used more complex algorithms that provided increased accuracy and flexibility. The Titan II used "delta" guidance, a simple guidance algorithm for low-power computers. In this guidance system, the algorithm attempts to keep the missile on a pre-computed path, using a third-order polynomial to steer back to the correct path.

The Titan IIIC required complex guidance software since the flight went through multiple stages. A typical Titan IIIC mission put a satellite into a geosynchronous orbit at an altitude of 19,323 nautical miles. To do this, the rocket launched and ascended to a parking orbit between 80 and 235 nautical miles, using Stage 0 (the boosters), Stage 1, and Stage 2. The rocket then used Stage 3 to move to an elliptical transfer orbit with an apogee of 19,323 nautical miles. Another rocket burn put the vehicle into a circular orbit at this altitude. Finally, the payload separated from the rocket, putting the satellite into geosynchronous orbit. The point is that the guidance computer needed to perform many different guidance tasks, as well as controlling the various rocket stages.

The overall Titan IIIC guidance algorithm is called "explicit" guidance, where an explicit solution is computed during flight to reach the desired end result. (I haven't been able to determine if the Titan II switched to this guidance algorithm when the computer was upgraded.)

For an overview of guidance algorithms, see this document (p225) as well as Titan IIIC Guidance. For a more humorous explanation, see "The Missile Knows Where It Is At All Times." ↩

-

For more information on the physical characteristics of the Magic 352 computer, see Space Tug Equipment Data Bank page 58. ↩

-

It's difficult to sort out the permutations of Delco, AC Spark Plug, AC Electronics, AC Delco, and so forth. AC Spark Plug started in 1908 and became a division of General Motors in 1927. It was named after Albert Champion who also started Champion spark plugs. AC Spark Plug's Milwaukee manufacturing facility became AC Electronics in 1965, with a focus on inertial navigation (details). Meanwhile, Dayton Engineering Laboratories (Delco) was founded in 1909, and acquired by General Motors in 1918. GM's defense systems laboratory was started in 1962 and merged into Delco Systems Operations in Goleta (where this Titan guidance computer was built). In 1970, the Delco Radio Division and AC Electronics Division of General Motors Corporation were consolidated into a new Delco Electronics Division. In 1985, GM purchased Hughes Aircraft and merged it with Delco to form Hughes Electronics, which was sold to Raytheon in 1997. ↩

-

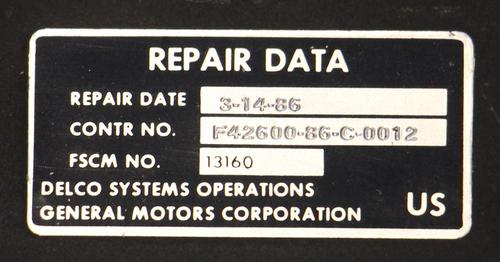

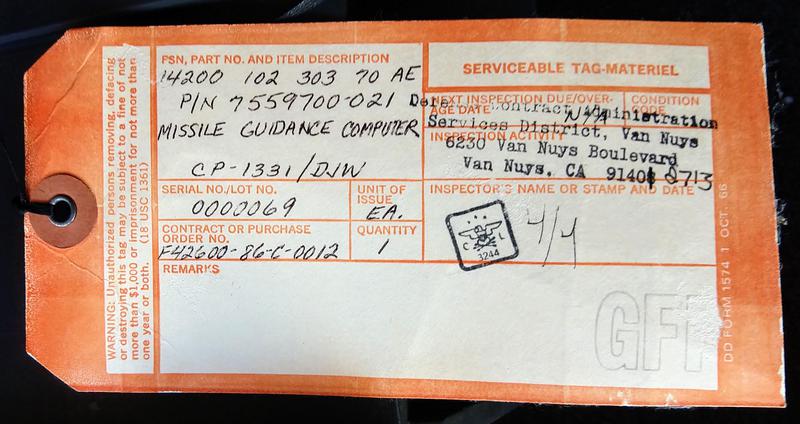

The photo below shows the label on the computer, serial number 69. The "CP-1331/DJW" designation is a military component designator. The "CP" indicates a computer unit and 1331 is the model number. The "DJW" is an "AN System" military designation for a guidance system, specifically "Missile/Drone Electromechanical Flight Control Equipment".

The label from the Titan missile guidance computer.The computer also has a repair label showing it was last repaired on March 14, 1986.

The repair label on the computer.Each removable panel was protected with tamper-proof seals:

The sticker says "DO NOT BREAK SEAL". I broke the seals.The computer also had an attached service tag. The penalty for removing the tag is up to a year in prison, so it's worse than a mattress tag.

Serviceable Tag—Materiel. -

At the back left of the computer is a fill valve, used to pressurize the computer with nitrogen to 5 PSI above ambient. The valve appears to be a Schrader valve, the same as on an automobile tire. Before opening the computer, I vented the nitrogen and found that the computer was still pressurized decades later. ↩

-

The underside of the computer has an access panel for the cables in the central section. The photo below shows the view looking up through this access panel, showing the connectors on top of the computer, as well as the cables attached to them. This part of the computer is almost entirely empty space. The backplane for the interface side of the computer is visible in the bottom of the photo; the boards plug into the other side.

View into the central part of the computer showing the cabling.Most of the connectors on top of the computer are 61-pin circular MIL-Spec connectors. Note the keying pins sticking out of the circular shell below. Each connector has different keying to prevent attaching a cable to the wrong connector. The power input uses a 31-pin connector with larger pins that support higher current.

One of the connectors on the computer, labeled "J5".Most of the connectors currently have yellow plastic caps, while two have metal screw caps. I think that the metal caps are for test connectors that would remain covered in flight, while the plastic caps are temporary covers for connectors that would be cabled up in flight. The test connectors are wired to the digital side of the computer. ↩

-

I couldn't find many details on the Magic 352 computer, but there is some information in Guidance and controls for an Interim Upper Stage (IUS) page 339, and Titan IIIC Guidance page 15. ↩

-

I'm a fan of core memory and have written about the core memory in the Saturn V LVDC, the Apollo Guidance Computer, the IBM 1401, and the IBM System/360, if you want to read more about core memory. ↩

-

The wiring topology of the core memory module is worth noting. Because the parity end board has half of a regular core plane, it has 64 Y wires instead of 128. These 64 wires pass through the cores and then do a U-turn, returning to the next plane as the other half of the 128 wires. The 128 X wires, on the other hand, pass through the cores and then are terminated on the board. The board at the other end terminates the 128 Y wires (as two logical groups of 64) and the other end of the 128 X wires. Both boards have numerous diode packages for these wires. ↩

-

I calculated that the computer's two core memory modules hold a total of 16K words of 24 bits plus parity. This matches the Magic 352 memory size specified in this article. However, another document says the Titan IIIC computer has 16K of memory with 2K erasable (it's unclear if these numbers are bytes or words). There's a patent related to the Titan computer describing a core memory that combines DRO (destructive read out, i.e. RAM) and NDRO (non-destructive read out, i.e. ROM). The ROM is implemented by omitting cores to store 0 bits. I believe the ROM was an optional feature, so you could get 14K of ROM and 2K of RAM, for instance. ↩

-

The Gemini space flights (1964-1966) used a Titan II GLV missile, but the guidance system was entirely different. Gemini removed the Titan II inertial guidance and replaced it with a General Electric Mod IIIG radio guidance system, for guidance from the ground (details). The Gemini capsule contained the Gemini Guidance Computer (OBC), built by IBM. ↩

-

The Carousel IMU got its name because the inertial platform rotated at 1 RPM (like a carousel) to reduce drift errors (details). Here is a photo of a commercial Delco Carousel. The Titan computer was connected to an IMU that was probably similar inside, but packaged in a black box that resembled the computer but more cubical. ↩